Assertion system verilog

Hence assertions are used to validate the behavior of a . Immediate Assertions.Special SystemVerilog Assertion features Assertion system tasks and functions Assertion binding Assertion simulation semantics 13 Verilog Does Not Have An . Coverage statements ( cover property ) are concurrent and have the . Immediate assertion example.Assertions are a mechanism or tool used by HDL’s (VHDL and Verilog) to detect a design’s expected or intended behavior.SystemVerilog Assertions.Verilog doesn't support assertions.Chip/system interface assertions (chip/system interface intent) Commercially available standard bus assertion VIPs can be useful in comprehensive check of your design’s adherence to std. In this article we will learn about the assertions and need for it.and Lisa Piper VhdlCohen Publishing

Getting Started With SystemVerilog Assertions

Nowadays it is widely adopted and used in most of the design .SVA, the assertion temporal language portion of SystemVerilog, draws on the strengths of three languages: PSL from Accellera with roots in Sugar, a language used at IBM, VERA .SystemVerilog Assertions Handbook, 4th Edition is a follow-up book to the popular and highly recommended third edition, published in 2013. Assertions, 16. Before System Verilog assertions were present as part of the HVL.SystemVerilog language consists of three very specific areas of constructs -- design, assertions and testbench.

In this blog post, we will explore various assertion control functions in Verilog and SystemVerilog, diving deep into how you can use them . (1) Verilog是一种过程语言,因此并不能很好地控制时序。. Syntax: The result of the coverage statement shall include. The next piece of the puzzle is a must stay high until b is asserted. The course is packed with examples, case studies, and hands-on lab . SVA Built-In Methods.This book provides a hands-on, application-oriented guide to the language and methodology of both SystemVerilog Assertions and SystemVerilog Functional Coverage.1 PCI Arbiter assertions 279 6.

Introduction to SystemVerilog Assertions

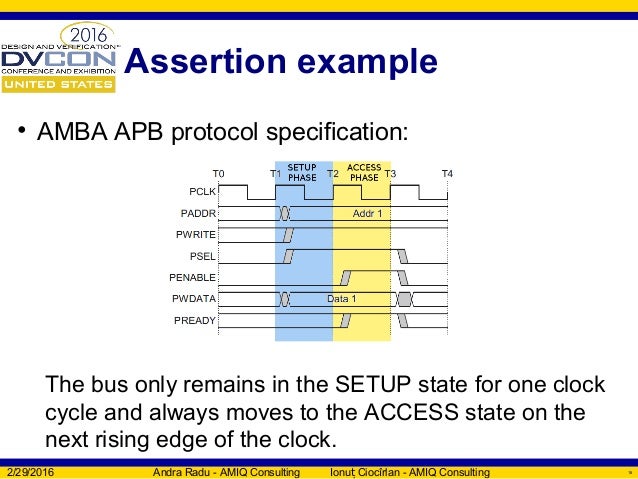

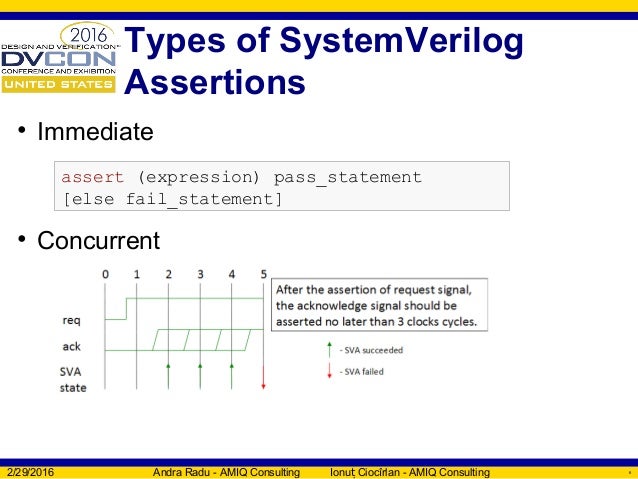

Traditionally, engineers are used to writing verilog test benches that help simulate their design.2 Overview, P364, Rev 2017: “An assertion appears as an assertion . This 4th Edition is updated to include: 1. Using a simple arbiter as an example verification target, we introduce each of the basic concepts of SVA. There are two types of assertions (both implemented by SystemVerilog): immediate assertions and concurrent assertions. A complex property can be phrased with multiple sequence blocks. In this paper we show that there are several compelling reasons for synthesizing . The number of times property attempted, failed, or succeeded (even due to vacuity which is applicable only for implication operator).System Verilog Assertions Simplified - eInfochipseinfochips.Introduction to SystemVerilog Assertions | Siemens Verification Academy. protocol such as PCIe, AXI, etc. systemverilog assertion作为systemverilog引入的重要特性,在功能仿真及形式验证中有着重要的作用。. Cite this chapter. Changing the structure or design of a module using SystemVerilog Parameters. The inconsistency in the definition of the building blocks of SVA that may lead to confusion can be read from the P1800, where assertion is defined as:. For implication, a false antecedent is a vacuous pass.6 Summary on SVA for standard protocol 283 CHAPTER 7: CHECKING THE CHECKER 285 7. Variable delay in SVA. SystemVerilog Assertions (SVA) form an important subset of SystemVerilog, and as such may be introduced into existing Verilog and VHDL design flows. COEN 207 SoC (System-on-Chip) Verification Department of Computer Engineering Santa Clara University Introduction • Assertions are primarily used to validate the behavior of a design • Piece of verification code that monitors a design implementation for compliance with the specifications

[SystemVerilog] Assertion : 네이버 블로그

Temps de Lecture Estimé: 6 min

SystemVerilog Assertions Tutorial

Here we'll use the throughout operator.

This would cause you to ignore bad behavior.2 Overview, P364, Rev 2017: “An assertion specifies a behavior of the system”.

Implication Operator.

SystemVerilog Assertions.

An assertion also provides .

SystemVerilog Assertions

The following sections explain what they mean.Covers both SystemVerilog Assertions and Sytem Verilog Functional Coverage language and methodologies; Provides practical examples of the what, how and why of Assertion Based Verification and Functional Coverage methodologies; Explains each concept in an easy to understand, step-by-step fashion and applies it to a real example Generate Overview.Here is where System Verilog ‘bind’ comes into the picture. Ended and Disable iff.Systemverilog之SVA(一). Lazy instantiation of module items using a for-loop. (2) Verilog是一种冗长的语言,随着断言的数量增加,维护代码将变得很困难。.

Using SystemVerilog Assertions in RTL Code

Assertions are a useful way to verify the behavior of the design.Assertion is a very powerful feature of System Verilog HVL (Hardware Verification Language).Preface i SystemVerilog Assertions Handbook, 4th edition and Formal Verification Ben Cohen Srinivasan Venkataramanan Ajeetha Kumari. module my_module; assert property (@(posedge (mod_clk & . SVA Building Blocks.The way you wrote your assertion, it would only trigger checks if the throughout sequence also happened after rose(a).This video is all about the introduction to SVA(System Verilog Assertions, What are assertions, Why to use assertions, Who will write the assertions, some ad.

SYSTEMVERILOG ASSERTIONS FOR FORMAL VERIFICATION

Assertions are a powerful tool used in the design and verification of digital systems to formally verify the behavior of a system. RTL/gate/transistor level.SystemVerilog Assertions (SVA) SystemVerilog (proliferation of Verilog) is a unified hardware design, specification, and verification language. System Verilog . The series or expressions spread over one or more clock cycles is called a sequence.먼저 Assertion의 이름을 써준다.

SystemVerilog Assertions and Functional Coverage

Assume and Cover Statements

7k次,点赞5次,收藏16次。断言(System Verilog Assertion 简称SVA)可以被放在RTL设计或验证平台中,方便在仿真时查看异常情况。一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。断言通常被称为序列监视器或者序列检验器,是对设计应当如何执行特定行为的描述 .There are two main types of SystemVerilog assertions: (1) immediate and (2) concurrent assertions.

System Verilog Assertions

Concurrent Assertions: Assertions are primarily used to validate the behavior of a design.

Conditional Statement in Assertion Property

SystemVerilog Generate Construct

The Generate construct is a very useful tool. Assertions are used to check design rules or specifications and generate warnings or errors in case of assertion failures. Assertions help designers to protect against bad inputs & also assist in faster Debug.System Verilog Assertions. Nowadays it is widely adopted and used in most of the design verification projects. Some tools support PSL, which places the assertions in comments but this is non-standard.

Download book PDF. First Online: 10 October 2019. You'll commonly see it used for these 3 purposes. (3)语言的过程性这一本质 .Nや[*N]でシーケンスの遅延や連続繰り返しが表される。この遅延値や連続値を可変にした以下の様なプロパティを書きたい事も多い。しかし、Nは固定値である必要があり、SVAで以下のような .2为什么使用 System Verilog断言 (SVA) 虽然Verilog可以很容易地用来实现一些检查,它仍有一些不足之处. The property gets attempted on each clock cycle. Readers will benefit from the step-by-step approach to functional hardware verification using SystemVerilog Assertions and Functional Coverage, which will enable . System Verilog introduced . 괄호속 적어놓은 조건 (expression)이 True일때 수행되는 문장이고. The behavior of a system can be written as an assertion that should be true at all times. Assertions are critical component in achieving Formal Proof .

Assertions in SystemVerilog

Using generate with assertions for Functional and Formal Verification.SystemVerilog Assertions (SVA) Ming-Hwa Wang, Ph. A new section on testbenching assertions, including the use of constrained-randomization, along with an explanation of how constraints operate, and with a .In SystemVerilog there are two kinds of assertions: immediate (assert) and concurrent (assert property).System Verilog Assertion Constructs (1) 11 Nov 2023. The System Verilog language integrates the specification of assertions with the hardware description.

![]()

Assertions provide a better way to do verification proactively. Since the property under the else evaluated to pass, the .Last updated on Apr 21, 2023.

Mastering Assertion Control in Verilog and SystemVerilog

They allow designers to define the intended .In reply to Reuben:.SVA bind file requires assertions to be wrapped in a module that includes the port declaration, So now let’s understand this with a small example to understand basic things on how to use SVA bind

SystemVerilog Assertions

and Lisa Piper VhdlCohen Publishing In this session, you will learn the benefits of using SystemVerilog assertions including; when and where . Repetition Operator.

SystemVerilog Assertions应用指南 第一章

Download book EPUB.Verilog; SystemVerilog; VerilogHDL; assertion; SVA; Last updated at 2024-02-28 Posted at 2024-02-11. Bus interface will be in “wait” state whenever the master and slave are not ready. It discusses SVA methodology, immediate/deferred assertions, Concurrent assertions and its operators, .Introduction to systemverilog assertions. Assertion is a very powerful feature of System Verilog HVL (Hardware Verification Language).The cover statement is used to gather coverage information for the specified sequences or properties.

YosysHQ AppNote-109 documentation

그리고 assert를 쓰고 조건을 (expression) 안에 넣어준다. Assertions can be written whenever we expect certain signal behavior to be True or False.SystemVerilog Assertions : Assertions are a useful way to verify the behavior of the design. The easiest way to mimic C-like assertions is probably a `define since . Generally, you create an SVA bind file and instantiate sva module with the RTL module. The number of times a sequence attempted and matched.断言(System Verilog Assertion 简称SVA)可以被放在RTL设计或验证平台中,方便在仿真时查看异常情况。一般在数字电路设计中都要加入断言,断言占整个设计的比例应不少于30%。断言通常被称为序列监视器或者序列检验器,是对设计应当如何执行特定行为的描述,是一种嵌入设计检查。