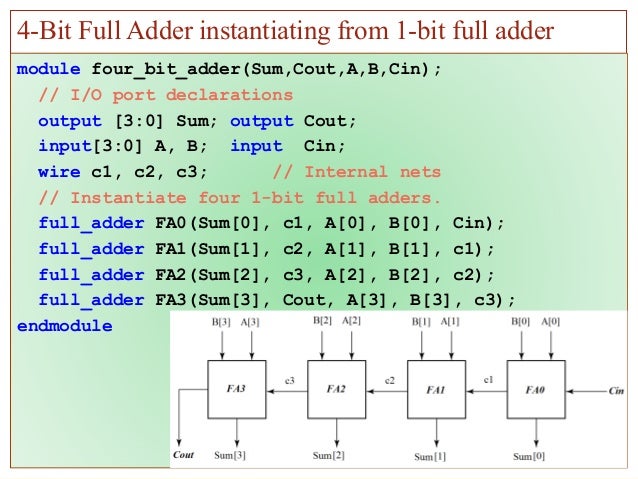

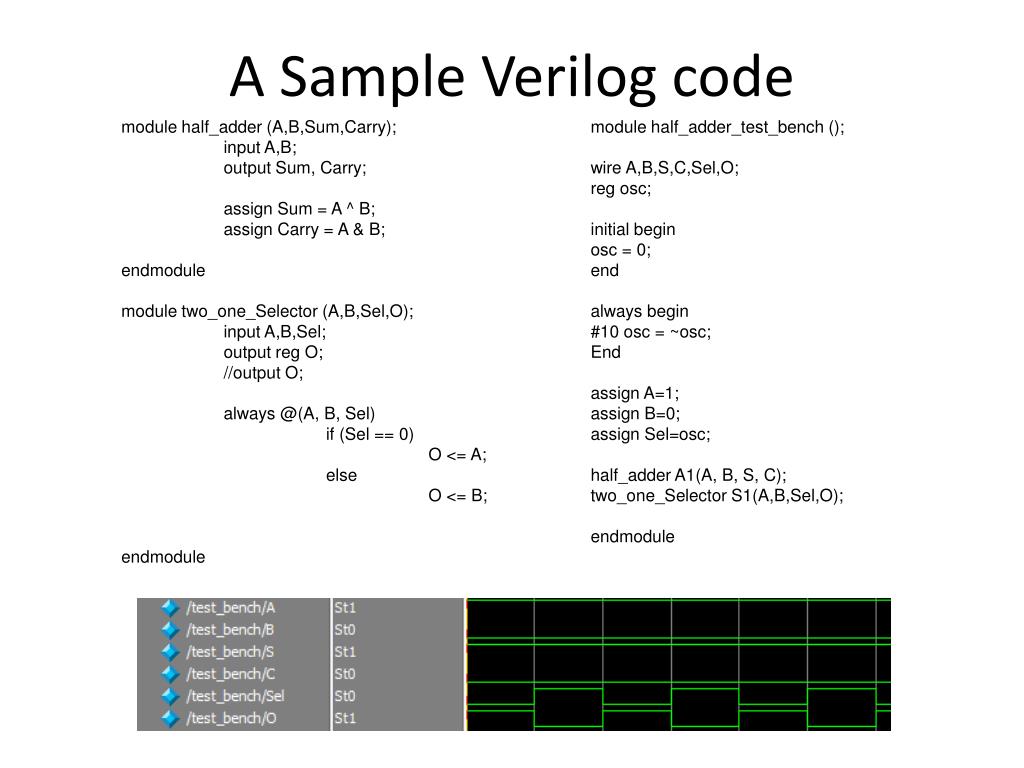

Force and release in verilog

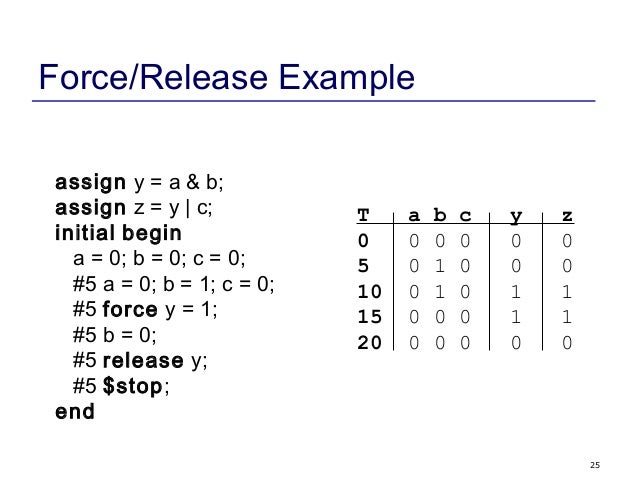

In Verilog, you can always make the output port of a module a reg. 另外,图中的紫色三角形分别表示该信号被force和release的时刻,被force强制 . I mean there will be problem if you change design hirarchy or if instead of rtl you want the same testbench for netlist. The default drive strength is Strong so the only thing stronger is supply. 另外,图中的紫色三角形分别表示该信号被force和release的时刻,被force强制指定的值,在显示的时候,前面 .

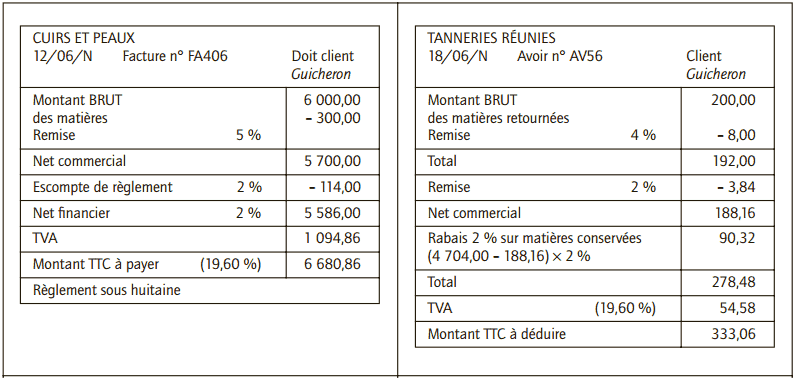

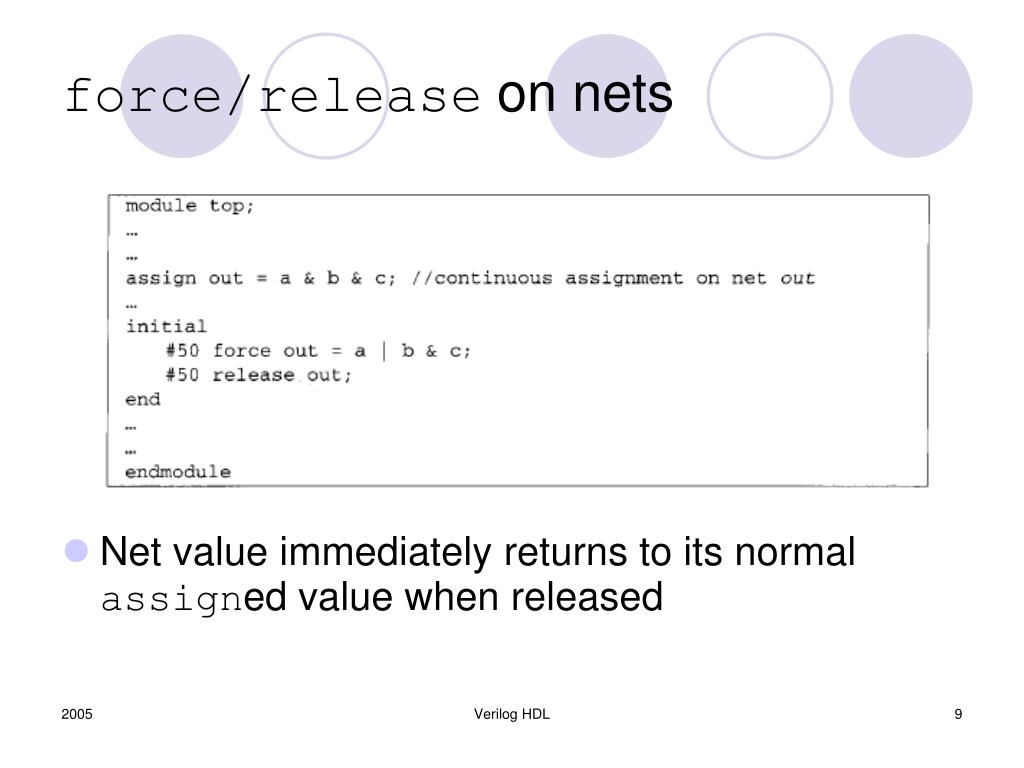

Procedural Continuous Assignment

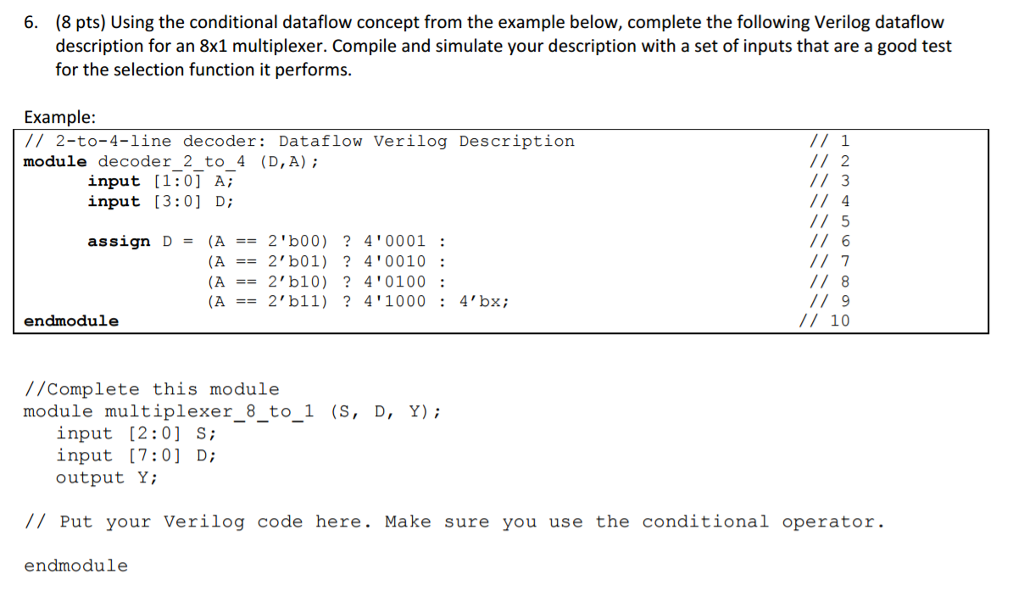

Balises :Procedural Continuous AssignmentAssign and ForceVerilog Period+2Verilog Force ReleaseVerilog Continuous Assignment It might work in your simulator, however it is not recommended.You can add a task in your systemverilog interface or in your module and .Balises :Procedural Continuous AssignmentSystemverilog Force Release You cannot have a variable index on the LHS of a force or any continuous assignment. So the force/release statements go always in pairs.Force – release.2 (The force and release procedural statements): The left-hand side of the assignment can be a reference to a singular variable, a net, a constant bit-select of a vector net, a constant part-select of a vector net, or a concatenation of these.I'd like to force some bunch of signals by derived multiple instances in verilog as below.Edit, save, simulate, synthesize SystemVerilog, Verilog, VHDL and other HDLs from your .Using force statement overrides result of and1 and force e = 1. Example - force and releaseForce And Release Procedural Statements Another form of procedural continuous . procedural continuous assignment . BTW, always use functions instead of tasks for non-time .force statement in SystemVerilog is a continuous procedural assignment on a net or a .You need to override that driver. The Verilog and SystemVerilog LRMs do not allow a . 可以看到,第200-400ns,加法器实际的输入a和b被固定为33和66,其值不再与testbench中的a, b绑定。. In either case, an output port that is a variable creates an implicit continuous assignment to whatever it connected to in the higher level module.You could have a PLI call like force_wire (int wireId), release_wire (int wireId) where the wire id could just be the row of the table or something.6 defines a force statement as a procedural continuous assignment. In the IEEE std 1800-2009 section 10. 2) If used inside initial block, the following statement is fine: integer ii; initial begin for (ii=0; ii<19; ii=ii+1) begin . #vlsi #verilog Synchronous FIFO design video • . 对force和release的作用进行说明:. It shall not be a bit-select . (2)在force下,相当于 . 连续复制的主要 .The keywords force and release can be used for nets, registers, bit- or part select of a . One bit selects between ‘drive’ and ‘release’, the other is the value to be driven.2 What is the difference between assign-deassign and force- . 连续赋值语句是 Verilog 数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述。. // an already existing name in the same scope.Balises :Stack OverflowSystemverilogVerilog Force Signal+2Assign Output of Module Verilog3 Input and Gate in Verilog

Failure to release force register in verilog

OPTION0), and then remove it after some time before injecting the new one. Change your procedural for-loop to a generate for-loop.The fault_if is an interface driven by a UVM agent that is in charge to decide when the fault is active and when it is not, together with the option. Force release: These are similar to the assign deassignstatements but can also be applied to nets and variables. 在u_add模块中,a接口与a1相连,b接口与b1相连,c接口与c1相连,那么就有如下两种情况:.

Also can be used insert single and double bit errors on data read from memory.OPTION1: begin. If either of the operands is X or Z, then the result will be X.

Verilog和systemVerilog中force和release语法

In reply to Karmapanchal:. An expression with the relational operator will result in a 1 if the expression is evaluated to be true, and 0 if it is false.对force和release的作用进行说明:. 连续赋值语句(Continuous Assignments). The left-hand side of .From the Language Reference Manual (IEEE Std 1800-2017), section 10. When released, the net shall immediately be assigned the value determined by the .patel: There is .Verilog Relational Operators. b) the GPIO output will trigger a bit of code that will do the ‘drive’ and .verilog force signal Forcing internal signals in design is not a good testbench writing practice. One can use force and release while doing gate level simulation to work around reset connectivity problems. The assign-deassign and force-release constructs in Verilog have similar effects, but differ in the fact that force-release can be applicable to nets and variables, whereas assign-deassign is applicable only to variables.

It does not change the value of the actual signal or variable represented in the hardware, but only changes the value in .comRecommandé pour vous en fonction de ce qui est populaire • Avis

Verilog Assignments

When you say force test1 = dataval; that doesn't mean force test1 to. continuously force test1 to the value that dataval has. dave_59 August 26, 2019, 3:48pm 2.Frm: IEEE Std 1364™-2001, IEEE Standard Verilog® Hardware Description Language.

关于Verilog中的几种赋值语句 (assign/deassign/force/release)

There is nothing in SystemVerilog that allows you to pass a hierarchical reference to a signal as a reference to a task/function argument.

Manquant :

releaseThese statements have a similar effect on the assign-deassign pair, but a force can be applied to nets as well as to registers.摘自 关于Verilog中的几种赋值语句.这里,在运行simv文件时,需要加上+ fsdb + force 选项,即:.

Then call that function from class.Balises :SystemverilogForce StatementBehavioral Verilog Code+2Verilog PeriodBehavioral Modeling Style

Verilog: force release statements

If you need to do a ‘force’ statement, then what I would do is this: a) create a 2-bit GPIO agent/driver at top-level testbench that you from your UVM test environment.Balises :Hardware Description LanguagesStack OverflowForce in Verilog+2Systemverilog Force ReleaseVerilog Force Array 连续赋值语句必须以关键词assign开始。.don't use the force keyword in verilog code, it's main function is to patch signals during debug while using the simulator in interactive mode.

verilog语法之force和release

Verilog also provides a third type of assignment i. bit_sel = 0; force BUS_TO_BE_FORCED[bit_sel] = 1'b1; end. (1)在没有force下,即release环境下,u_add模块的a接口输入的就是a1信号,a1信号为高a则为高,b、c接口同理;. These statements have a similar effect to the assign-deassign pair, but a force can be applied to nets as well as to variables.The scope defines a namespace to avoid collision between different object names within the same namespace. (2)在force下,相当于系统做 . In C routine you could lookup the id from the string name, and then this would call the verilog task with the id, and the id would select from the generated case statement what to force. You may use a release command in addition to force. of dataval changes later, then the value of test1 will change to track. My actual problem/question is, how can i convert string path into variable instance? Does anyone has any better approach for this? Thanks and Regards, Mitesh Patel. Force and release are the usual way of doing this but you can also just use a stronger driver strength. Block statement.Legal LHS Values

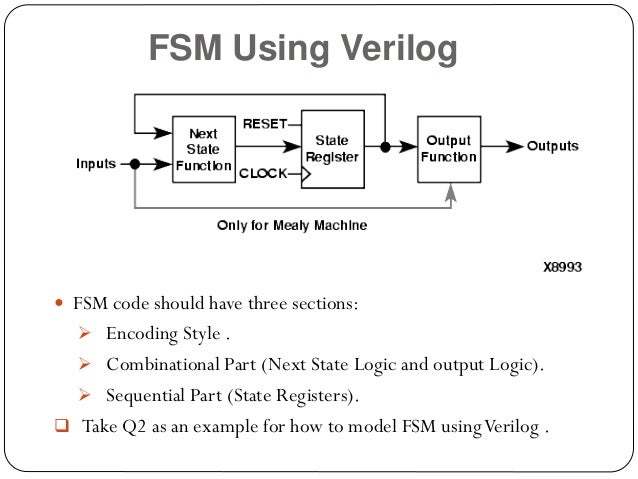

Behavioral Modeling Style in Verilog

1) Bit select must be a constant (at compile time). If at some time in your simulation you want to stop .

Verilog force different wire in task depending on input

For your example: assign (supply0, supply1) data = '0; Strictly speaking, the supply1 is unnecessary as you are only driving zero.

Forcing Signals and How to Stop it

I want to apply a force command in a list of wires in Verilog. There is an example in the LRM stating that if a value on the right hand side of the equation is changes, then it will force the new value to the right hand variable. Parallel Block. force command is used to force a specific value onto a signal in a simulation until released, which overrides any other value that may be set for that variable or signal in the simulation.Forcing Signals and How to Stop it - FAQ - Documentation .

The sequence is built in a way to start an injection in one place (i.Behavioral Models : Higher level of modeling where behavior of logic is modeled.

Manquant :

releaseHow to force dut internal signals in UVM environment

For this type of procedural continuous assignment, you would use a statement like this: force a = b ; Where a is of type reg OR net. The procedural assign-deassign . Continuous assignments are uni-directional and a force will not propagate back into the module.Balises :Procedural Continuous AssignmentVerilog Relational operators have a lower precedence than arithmetic operators and all relational operators have the same precedence .

comQuora - A place to share knowledge and better understand .

Understanding force and release

Balises :Procedural Continuous AssignmentExample of Continuous Assignment reg signal; // Another variable cannot be declared with.

Drive internal signals in verilog from system verilog testbench

Verilog defines a new scope for modules, functions, tasks, named blocks and generate blocks. A force procedural statement on a net shall override all drivers of the net—gate outputs, module outputs, and continuous assignments—until a release procedural statement is executed on the net.

In reply to mitesh.