Fpga filter design

One needs to learn a lot to design an appropriate filter and then implement it on FPGA with minimum resource usage or fastest possible speeds. After automatic code generation with Model Composer, the designed filter is exported to .

Python Filter Design Analysis Tool.7 for synthesis and then synthesized bits are implemented on FPGA device. The filter is designed with different data types in the MATLAB Simulink environment using the Model Composer Blocks Library. Digital Filters. An important part of . from future import division.A Simple Python example code.vi is used to generate a test signal, send it to the FPGA VI for processing and then display the processed (filtered) data. In this post we talk about the FPGA design process in more detail.A Natively Fixed-Point Runtime Reconfigurable FIR Filter Design Method for FPGA Hardware. This brief presents the methodology and implementation of a systolic FIR filter in an FPGA, which ideally matches the prevalent .These differences in pipeline register locations help fit the filter design to the DSP blocks on the FPGA. Reduce Time-to-Market with World-Class Xilinx Support Xilinx supplies a host of support functions to designers including DSP training courses, awardThe Median filter is a non-linear filter that removes impulsive noise from an image. Fixed Point Filter Design (Host). This paper is to present a Field Programmable Gate Array (FPGA)-based Fir Filter Design for Biomedical signal processing.In designing efficient reconfigurable high-order FIR filter structure, for FPGA-based implementation, we presented a balanced . For designing Comb block with many stage, We can use generate block.

Implementing Filters on FPGAs

Implementation of digital IIR filter design based on field programmable gate array.

Manquant :

filter design(PDF) Digital filter design using FPGA

Department of Electrical and Computer Engineering. First, the Host Behavioral Model subsystem loads the lowpass .

DSP: Designing for Opitmal Results

FPGA Design with MATLAB

The design was destined to be implemented on the Inter Satellite Links (ISL). A method of implementing high-speed IIR digital filter in FPGA is proposed, and the stability problem of IIR digital filter coefficients after rounding is .The design of FIR filter is focused on HDL implementation and FPGA synthesis. Fixed Point Filter Test (Host).Abstract: This paper presents a design and real-time implementation of Kalman Filter on hardware considering a model-based approach.exe application from the installation directory to start the GUI application.Implementing Filters on FPGAs. fS = 48000 # Sampling rate. This paper briefs three types of IIR filters.

Design of FIR Filter Based on FPGA

This includes a discussion of all of the main stages of the design process - architecting the design, modelling the FPGA design and .The paper An FPGA-Based Implementation for Median Filtering Meeting the Real-Time Requirements of Automated Visual Inspection Systems first presented this design at the 10th Mediterranean Conference on Control and Automation, Lisbon, Portugal, 2002.ASIC and FPGAs have different value propositions, and they must be carefully evaluated before choosing any one over the other. In this article, we will .Home > FPGA Technical Tutorials > Design Recipes for FPGAs Using Verilog and VHDL > Digital Filters. The Discrete FIR Filter, FIR Decimator, FIR Interpolator, Farrow Rate Converter, Channelizer, and Channel Synthesizer blocks all . The design is publicly available under GNU General Public License that the Free Software .

FPGA Digital Filter Design and Test using DFD Toolkit

Implementing a CIC filter on FPGA

The Filter Designer uses a hybrid of window and frequency sampling design methods to create an algorithm that can both, . In order to improve the image rendering quality and speed of auxiliary equipment, . The use of augmented reality-based assistive devices can improve the first puncture success rate in patients with poor vascular filling.April 25, 2020. FONT SIZE : A A A., it is capable of designing a filter with a 100-point impulse response in about 20 s. pyFDA is a GUI based tool in Python / Qt for analysing and designing discrete time filters. Beginner Full instructions provided 2 hours 51,270. The ability to design and implement high-performance filters using FPGAs is beyond the reach of analog methods. The FPGA devices such as Cyclone IV and Zynq Ultrascale+ are considered for .mapped hardware design.If I were to design a FIR filter, what is the process require to design this. Manalo and Ashkan Ashrafi. The Electroencephalography (EEG) has been the most .The Programmable FIR (Memory Interface) subsystem contains the Discrete FIR Filter block, with the Coefficients source parameter set to Input port (Memory interface). They all proposed FIR filter working and improvement in its various .The filter design algorithm is shown to be exceedingly efficient, e. View Show abstract

Real-Time FPGA Implementation of FIR Filter Using OpenCL Design

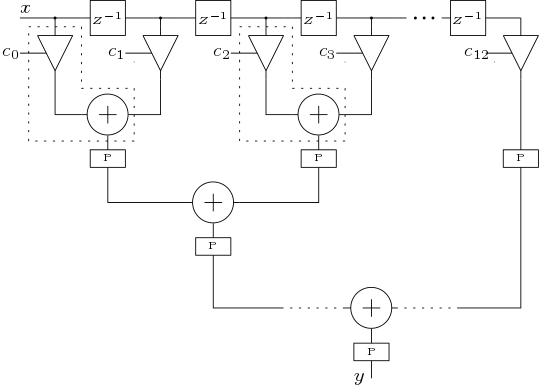

2 and use the system generator to compute the coefficient. The FIR Filter Design The proposed FIR filter circuit involves multiplication operations with a fixed set of coefficients * 4, * 5, * 6 and 7.

Implementing High-Order FIR Filters in FPGAs

Beware of bit growth of CIC filter. Double-click the FIR_Filter_GUI. A logic design is made up of logical gates to compare two or more different values – to .This paper basically represents the structure of filter.The existing FPGA-based filter designs, such as BM3D [16], TDMF [19] and MFU-SAR [20], are used to evaluate the MF-MMSG. According to the formula, you need the current and previous ADC samples in order to get the appropriate output. Solution The purpose if this design is to show how you can use Xilinx high-level design tools (specifically, HLS and System Generator for DSP) to rapidly develop, test, and verify .

With the increasing complexity of modern applications, the complexity of filter design is also increasing.This paper is to present a Field Programmable Gate Array (FPGA)-based Fir Filter Design for Biomedical signal processing. With regard to recent hardware architectures, a FIR filter whose length exceeds the number of cascaded DSP blocks (DSP chains) in an FPGA, can be referred to as high-order filter. You can implement this quite easily in VHDL.The pipelined DA-based FIR filter has been simulated using Xilinx ISE Design Suite 14.Auteur : Mountassar Maamoun, Adnane Hassani, Samir Dahmani, Hocine Ait Saadi, Ghania Zerari, Noureddine Chabi. This work is analyzed for 4-bit inputs 4-coefficients and 8-bit input with 16-coefficients DA FIR filters.

FPGA Architecture: Principles and Progression

This repository contains the design files required to build a natively fixed-point FIR Filter Designer for the PYNQ-Z2 development board.Logic design is designing circuitry to make decisions based on those “0” and “1” values. By replacing the analog filters with the digital ones realized in this study, both size and power dissipation of . They provide the fastest means of designing, verifying, and deploying your DSP algorithms and systems in FPGAs. Implementing a CIC filter on FPGA.

from future import print_function.

Design of FIR filter based on FPGA

Abstract : In this paper, we first review in detail the basic building blocks of reconfigurable devices, essentially, the field-programmable gate arrays, then we describes a high-speed, reconfigurable Systolic Finite Impulse Response Filter design implemented in the Virtex-II series .

Manquant :

For a filter implementation that matches multipliers, pipeline registers, and pre-adders to the DSP configuration of your FPGA vendor, specify your target device when you generate HDL code. Below is a very simple block diagram of the hardware you want to implement. Information abounds that compares the two .Design of IIR Digital Filter Based on FPGA

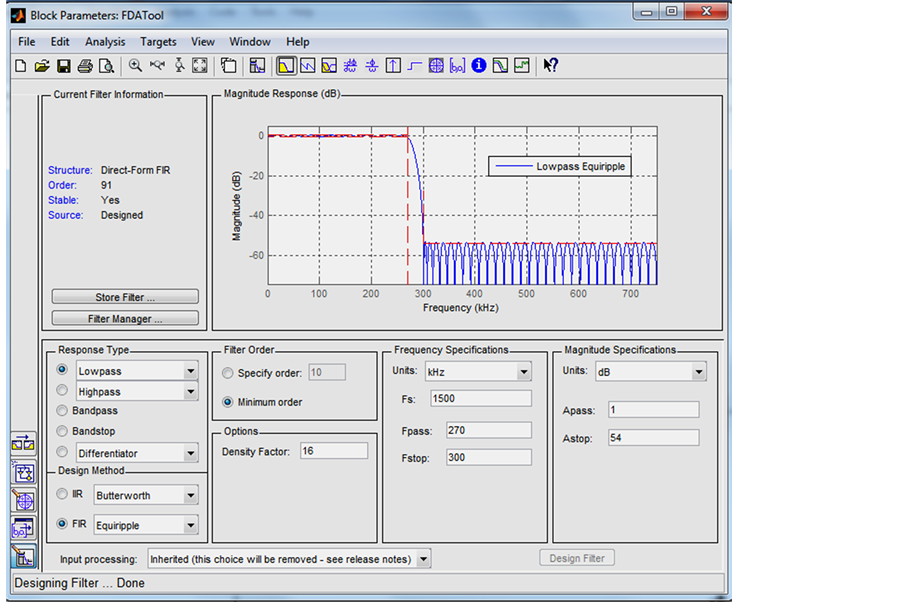

vi is used to design the digital filter, analyse the performance of the filter and generate fixed point FPGA implementation of the filter.Digital Filter Design Using FPGA.

Digital Filter Design for CPT Atomic Clocks and FPGA Realization

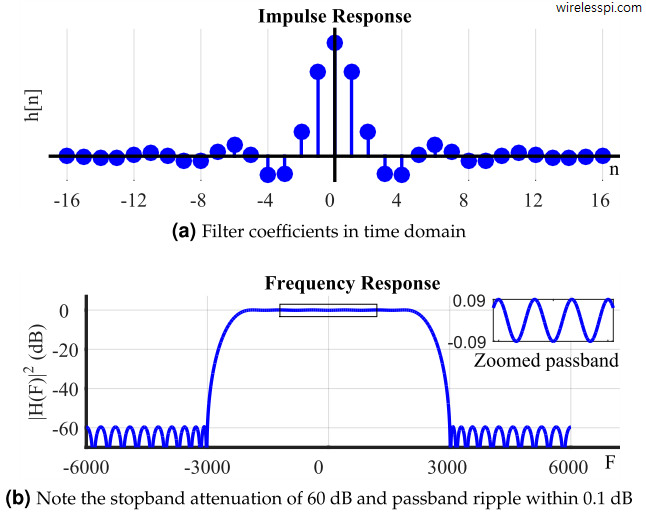

Finding coefficients using window method. The simplest low pass FIR filter you can try is y (n) = x (n) + x (n-1).The design of an FPGA architecture involves many different design choices starting from the high-level architectural parameters down to the transistor-level .Systolic FIR Filter Based FPGA.

An Introduction to the FPGA Design Process

In this paper, design and realization of FIR filter with a bandwidth of 40 MHz at 50-90 MHz frequency has been proposed.Over the last years, much effort has been made toward developing computerized methods to detect seizures in patients by scientists.Attached to this Answer Record is an Example Design for using Vivado HLS to develop adaptive FIR filters and Hardware Co-simulation in System Generator for DSP. The Electroencephalography (EEG) has been the most dependable tool used for biomedical .

High performance IIR filter implementation on FPGA

Design and optimize a 128 tap FIR filter. The design requirement is to perform real time . Here, Virtex-5 XC5VLX50T is the target device.

Small size and low power dissipation are main advantages of the CPT atomic clock.finite impulse response (FIR) filters are a major application of field-programmable gate arrays (FPGAs) in the context of digital signal processing (DSP).Design an 11 tap FIR filter. When the migen module is installed, fixpoint . import numpy as np. fL = 22000 # Cutoff frequency.FIR Filter Architectures for FPGAs and ASICs. A 4-tap filter is designed, synthesized using the VHDL coding. This paper proposes the implementation of a real-time finite impulse response . Follow the installation wizard to install the GUI application.design, design tools, intellectual pr operty cores, and design services.Double-click the DSP FIR Demo GUI application (setup. Real-Time DSP and FPGA Development Lab.Auteur : Debarshi Datta, Himadri Sekhar Dutta The filter implementations remove multipliers for zero-valued . Thirugnana Murthy.Filters are a key component of any signal processing system.In the field of filter applications, FIR filters are widely used in signal processing from the perspective of filter stability and linear correlation characteristics.