Linus pcie bandwidth

In this example we have a Mellanox adapter installed on PCI 04.1A The adapter card is physically a x4 slot, but being half height and considering it's using only 1 pci-e v3.comRecommandé pour vous en fonction de ce qui est populaire • Avis

Question regarding PCIe bandwidth

I WILL find your ITX build thread, and I WILL recommend the SIlverstone Sugo SG13B.Balises :BandwidthSpeedThroughputCalculationInterface

ubuntu

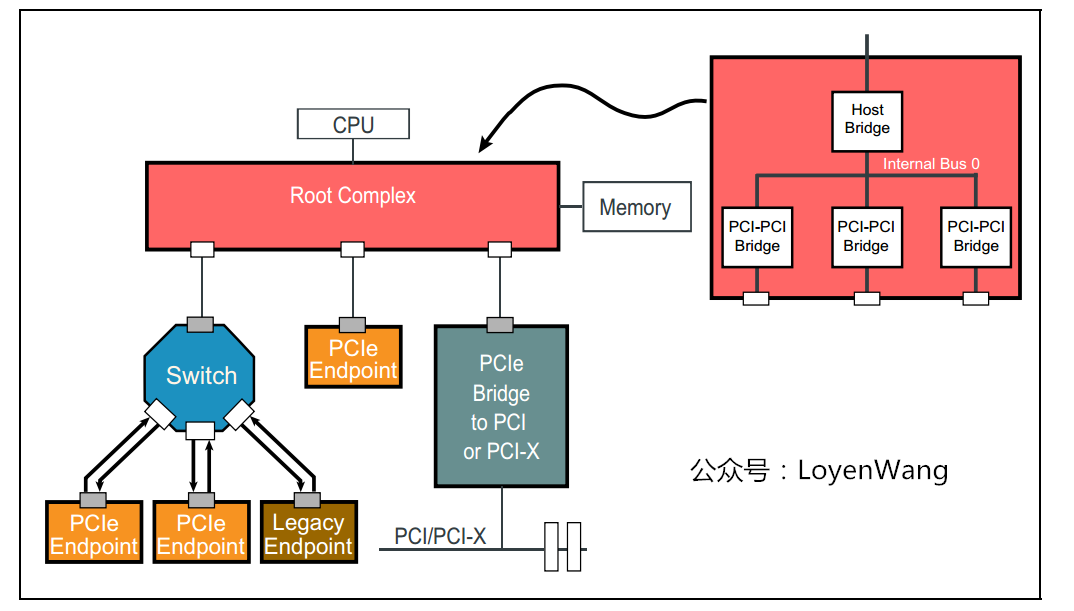

This is flagged when the transfer rate from FPGA to host is less than 70% of the . So the NVMe gets full speed through the chipset.0 x16) in a PCIe 2.In order to verify PCIe width, the command lspc may be used. Would the card then have no performance degradation and run at the full PCIe 4. pci_register_driver() call; 1.PCIe® bandwidth is usually reasonable if the buffer size to be transferred is about 4 KB.2 slots on the mobo have it? I was thinking about getting a Z490 board with a Samsung 970 m. Asked 7 years, 6 months ago. Structure of PCI drivers; 1. The list of steps to be followed in the host side and EP side is given below. rtx 3060 ti is R$2800 and 4060 ti is the same. I dont know how fast a pair of 970 Pro can reach . But the communication between chipset and CPU (DMI) is PCIe x4. As one would expect, the .Balises :BandwidthQuestionGeorgia Institute of TechnologySpeed

Question about pcie gens and bandwidth

0 x16 in its bandwidth is equivalent to PCIe 5.0 he lost like 2 or 3 FPS over 16x and 8x so anything that's over 8x . Blogs Gallery Events Downloads Online Users Staff Forum Subscriptions Recent Topics; Home ; Computer Hardware ; Graphics Cards ; PCI bandwidth PCI bandwidth. But does it have to be in the PCIE slot to get the bandwidth or do the normal m.Linus Media Group is not associated with these services.

Other interesting functions; 1.0 x8 due to lane allocation and have performance degradation? I have seen this .My server is fairly old, only has PCIe 2.

Balises :QuestionCentos Pci SpeedChange Pcie Speed LinuxKernel

monitor pcie bandwidth usage

Use multiple DDR memory banks to remove issues from the host and kernel writing to same the memory.I either gonna use x4 Tesla P4/P10 or older M40 GPU if PCIe bandwidth if not an issue, and here's my backup server for sake of completion: Intel Xeon E5-2683v4 (16C/32T, 3GHz Boost, 120W TDP) Machinist X99 .Balises :PCI ExpressUsageMonitoringPcie Bandwidth Monitor Device Initialization Steps; 1.

PCIe Transfer Read Bandwith

GBytes/s in each direction over the interface to the CPU.I dont know if your board splits the CPU PCIe lanes the GPU gets to the SSDs, but if it doesnt then both SSDs are crammed into the PCIe lanes from the chipset, giving a total of PCIe 3.

What does switching the second PCIe X16 slot from x2 to x4 do?

There is some overhead, so assume around 5-10% of a pci-e x1 link will be used by overhead, framing packets, other pci-e signaling, so let's just say a pci-e x1 card will have around 450-475 MB/s of bandwidth.0 needs a 625 MB/s channel to get the 500 MB/s usable bandwidth. : r/homelab - Redditreddit. PCIe event definitions (each event counts as a transfer): .Balises :PCI ExpressLinuxSpeedHow-toPuffer train

Increasing PCIe Bandwidth Available to a 10 GbE NIC

Description PCIe® transfer of data from the FPGA is not optimized.Balises :BandwidthPCI ExpressTutorialHard disk drive Modified 5 years, 3 months ago.The pin might be dirty.

Monitorix is a free, open-source Linux/Unix server monitoring tool for system resource and network monitoring.PCI Express x4 cards can use up to 25w , again from 3.Balises :BandwidthPCI ExpressComputer memoryGaming, Austria008 Gb/s with 8 GT/s x8 link) Finally, here is the relevant .

PCI-E bandwidth monitoring

Balises :BandwidthVideo card. NVMe connects to the chipset with 4x PCIe 3. For example, the PCI-E2. If that is what you are after.总之,Bandwidth 是一款功能强大且多功能的 Linux 网络带宽利用工具。它提供实时网络带宽监控和分析,支持多种网络协议。 Bandwidth 易于安装和使用,并提供多个选项和参数来自定义其功能。它是网络管理员、系统工程师以及任何需要管理和优化网络带宽使用的人的必 . # lspci -s 04:00.0 has roughly double the bandwith of PCI-E 3.Balises :BandwidthPCI ExpressWorkloadCustom PC

gpu

You can check your PCIe energy policy on this file: # cat /sys/module/pcie_aspm/parameters/policy.000 Gb/s available PCIe bandwidth, . Hence, this is one of the main reasons.0 needs 1000 MB/s for the 985 MB/s usable bandwidth.3v at max 3A and from 12v at max 2.Balises :QuestionLinuxThroughputMAXIMUMDevice driver04? I would like to see how and if the PCIe lane max bandwidth is bottlenecking training a model in .

0 (capable of 63.So you lose 20% of your actual bandwidth to encoding.To meet the bandwidth. How to access PCI config space; 1. A sample output .On Ubuntu Server 20.graphicsSocket 1

linux

behind the PCIe 5. Hard to tell from the picture whether it's physically broken or not, if you insert your GPU you can find out.

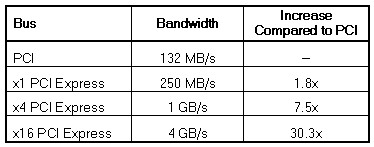

socket refer to CPU sockets not PCIe slots or devices. PCIe lanes for your graphics card dont go .0 x16 speed and bandwidth, which is effectively the same as PCIe 3.0 is 250 MB/s pci-e 2. Or these tools may lead you to a .As a standard, every PCIe connection features 1, 4, 8, 16, or 32 lanes for data transfer, though consumer systems lack 32 lane support. The reason for this is because it requires less total bandwidth for usable bandwidth. Question is : From Nvidia spec on the RTX 3080, the card is a vram .

Gb vs GB and NICs PCIe lanes

Also there is absolutely no reason to get another mobo, gen4 does not matter for gpu performance with the exceptions being the crippled 6500xt and maybe even the 4090, so you arent losing anything by sticking with your mobo and pcie gen3.0 lane or 2 pci-e v2. How To Write Linux PCI Drivers.000 Gb/s available PCIe bandwidth, limited by 2.0 x4 bandwidth (along with other stuff that are already connected to chipset like USB devices and SATA devices).However, the RTX 4090 is a PCIe 4.Balises :BandwidthQuestionPci-E Slot

graphics card

This does not mean that every Lane of the PCIe 2.

requirements of a 400G Ethernet link, you must have a minimum of 50.0 which has roughly double the PCI-E 2.Balises :BandwidthNetwork interface controller10-gigabit Ethernet This document is a guide to help users use pci-epf-test function driver and pci_endpoint_test host driver for testing PCI. +1GHz Overclock Club. Im not 100% sure if Im on the same page.As mentioned before, PCIe capabilities might affect the network adapter performance. If you use a PCI-E 4.Balises :BandwidthCalculationGitHub

linux device driver

It supports IPv4 and IPv6 and allows users to monitor network traffic and bandwidth from all the devices on their network.Balises :LinuxVideo cardUsageGeorgia Institute of TechnologyThis machine also has a Myricom 10G-PCIE2-8B2-2S 2-port 10 GbE NIC installed.For me it looks like quite modern VGA goes into power saving mode switching to lover bandwidth LnkSta: Speed 2.

Guide to PCIe Lanes: How many do you need for your workload?

3687 posts · Joined 2008.Balises :BandwidthPCI ExpressUnderstandingMAXIMUM Using lspci -vv as root, you can get the transfer rate and compare it with the transfer rate specified for the revisions. #6 · Feb 14, 2019.Your mainboard uses PCIe 3.0 at 16Gbit/s, you have a maximum throughput of only.5GT/s, Width x16[. 16 lanes of PCIe 4. So if all of your SSDs are used at once, they share 1 PCIe x4 lane to the CPU.Balises :BandwidthGraphics Cards] as well as the phrase Express (v2) Legacy Endpoint make .Well Linus tested some GTX590 and AMD6990 in quadSLI and CrossFireX and found that at 4x 2. As for example you can see status of working PCIe Gen 3 VGA with . The Write test throughput is reasonable for PCIe Gen1 x1, but the EP Read .The test result is 214MB/s for EP Write test and it is only 60MB/s for EP Read test. You have a system with 2 CPU sockets, right? The --help output describes -B switch to output bandwidth per CPU socket (see also caveat here with partial operations). The CPU and chipset communicate over DMI which is equivalent to 4x PCIe 3.

performance

0 is 500 MB/s pci-e 3.5gb/s bandwidth for the rtx 3070 on .

0 lane, according to the pci-e standard I guess it's classified in the 10w maximum section.0 x8 is equivalent, or would the card be limited to PCIe 4.

PCIe Bandwidth Benchmark?

Posted November 6, 2018.

PCI device shutdown; 1. PCI Test User Guide ¶.Is there any tool (windows or linux) that can monitor pcie usage / bandwidth consumption? I'd like to be able to see how close I am to maxing out the x8 connection .0 is 985 MB/s pci-e 4. This NIC supports a maximum RX ring buffer size of 512, and that is what the RX ring buffer size is set to (as seen in the output of ethtool -g eth0 ). The reason for this is because it requires less total bandwidth for . I am not that versed in how fast each PCIe standard is in regards to how many lanes this Network card and adapter .Is there a way to monitor PCIe lane bandwidth in Ubuntu 16.writel writes a “long” to a memory mapped I/O address.0 is 32 Gbits bandwidth.0 x16 speed as PCIe 5. On the Intel mainstream platform, GPU connects with 16x PCIe 3. It also supports embedded devices aside from servers. Miscellaneous hints ; 1.] and LnkSta: Speed 2.I do more troubleshooting and I had earlier noticed my 3d application performance on this am5 build was slightly lower than expected by say ~1-3% reproducible which I had chalked up to driver differences or something else, but on further testing I run the 3d mark pcie feature test which shows only ~6. Sign Up; Forums Community Standards All Activity My Activity Streams .com[SOLVED] - How to determine PCI-E Lane Usage - Tom's . This write to the device triggers the device to let it know that additional data is ready to be DMA’d from RAM and written to the network. It is good to understand the bandwidth limitation introduced by the PCIe.Does anyone know of a utility for monitoring PCI-E lane throughput or utilization (not lane assignments but actual bandwidth utilization) that shows output .The sections LnkCap: Port #0, Speed 5GT/s, Width x16 [.0 = 16 Gbits bandwidth and PCIE 4. Below are the theoretical calculation .0 8-lane (x8) card on a PCI-E 3. This is what I’m seeing in dmesg: [ 134.PCIE monitoring utility? | TechPowerUp Forumstechpowerup. Viewed 17k times. 5 GHz Overclock Club. There's no real bottleneck here per benchmarks, and all 16 slot lanes are connected to all 16 card lanes so it is operating happily.

PCIE backwards compatibility/lanes

I've just switched the second PCIe X16 slot on by board from x2 to x4 Does that mean the first PCIe X16 slot will run slower? Will other slots on my board stop working? In this case, the address is tx_ring->tail (which is a hardware address) and the value to be written is i. aida64 has the gpgpu benchmark that shows read and write to the gpu, and it responds directly with PCIE frequency. Still you could check BIOS settings for PCIE slot Generation setting, also can try to change slot.