Vhdl functions vs procedures

the default for in parameters is constant. Whereas in VHDL, each time you call a function, .

vhdl functions/procedures constant arguments

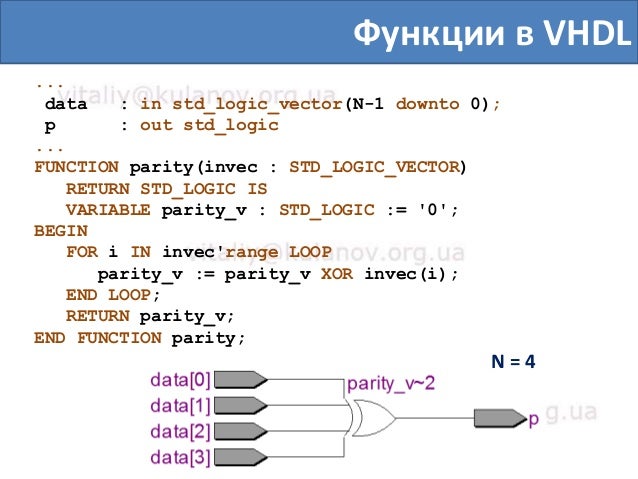

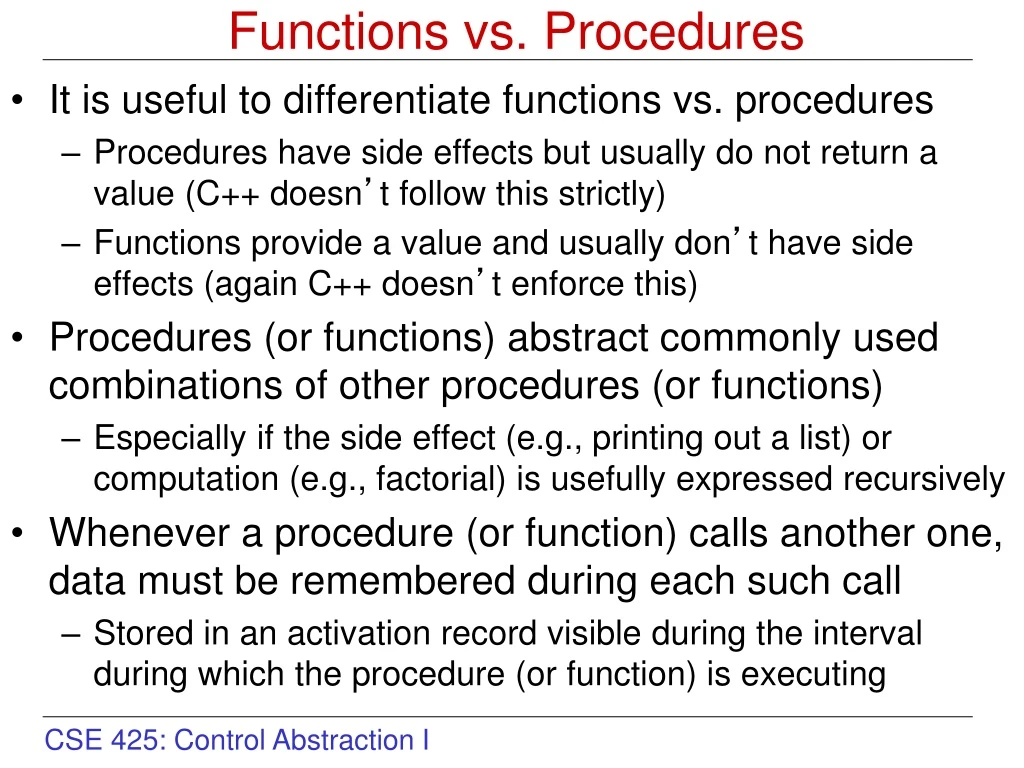

comFunction – VHDL GUIDEvhdlguide. Some coding styles . These are used to partition large behavioral descriptions into modular sections.A procedure declared within a process can access any signal within the scope of that process. Many people and companies use functions and procedures in synthesizable code. The function call follows the function name, with any required input .VHDL supports two kinds of subprograms (functions and procedures) that greatly help to improve the description, scalability and reusability of the code. The field of electronics, which in a way is its own society, also utilize languages that are specific to its members. In this post we look at how we use generics and generate statements to write reusable VHDL components. No assignment operator is needed.differently than those in C language. They are both synthesizable so implementation is . They help in creating organized and structured .Functions exist only in math, and they represent what is knowledge.

VHDL 2008 Generic Functions/Procedures

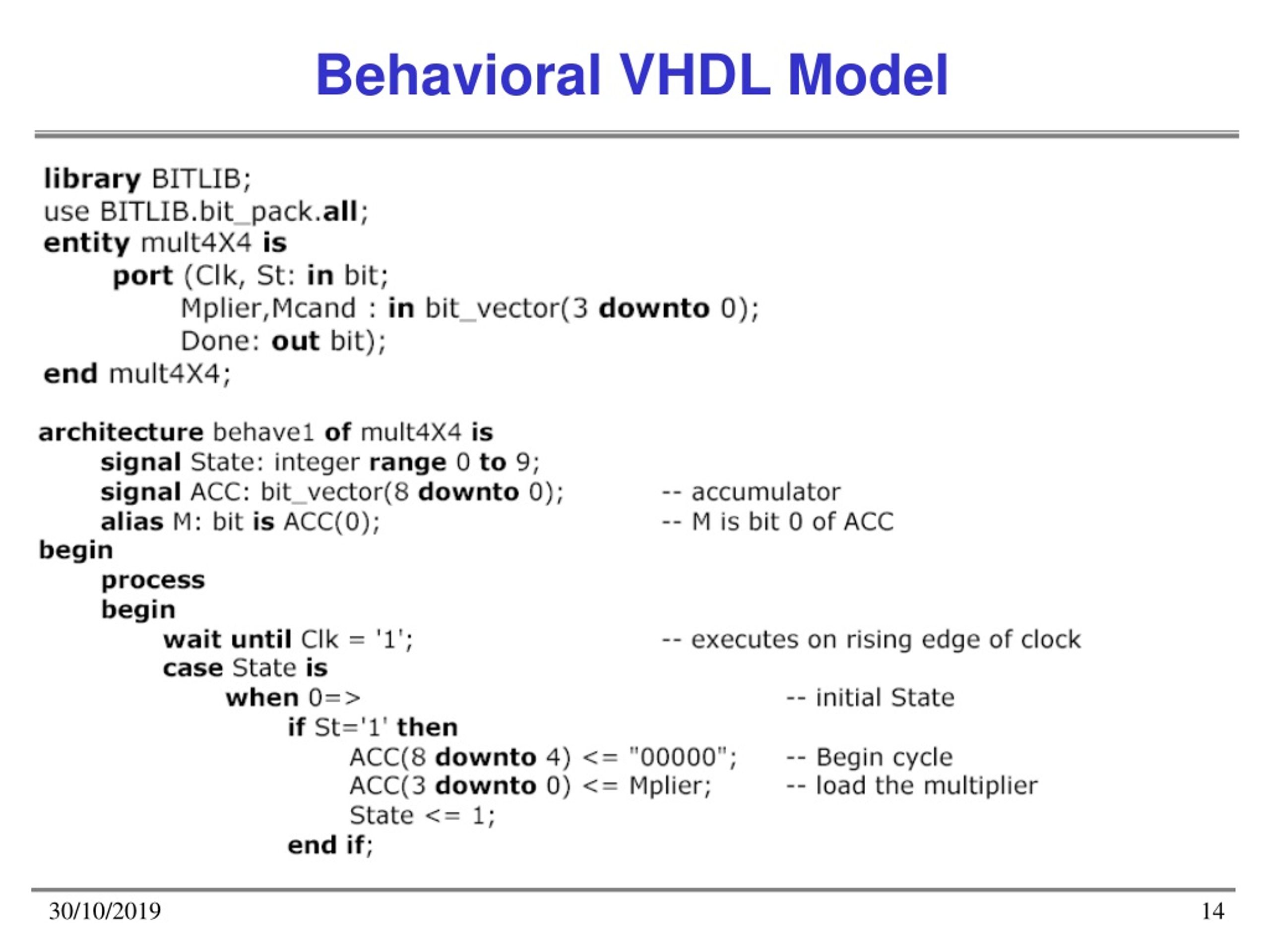

For synthesis, think small pieces of hardware (like Mux2, Mux4). signals), so surely it can be used in a .

Use of functions,procedures in vhdl

sequential statements.With VHDL however, it appears that there are three ways of breaking down a design: entities, procedures, and functions. Functions are equivalent .This blog post is part of the Basic VHDL Tutorials series. Should you claim your shown code is function consider the .Include to post we look at subprograms, which allow us to create reusable code, and packages. Functions in vhdl make the code easy to maintain and read.Subprograms, packages and libraries.

Please, clarify the concept of sequential and concurrent execution in VHDL

SUbprograms can be used in behavioral .3 Process statement: A process statement defines an independent sequential process representing the behavior of some portion of the design.1 SUbprograms In VHDL, the term subprogram refers to a function or a procedure. Both procedures and functions written in VHDL must have a body and may have declarations. Para 12: The execution of a process statement consists of the repetitive execution of its sequence of statements.

How to use a function in VHDL

Exercise

Functions in VHDL: A Comprehensive Guide

Functions play a crucial role in VHDL programming as they allow for code modularity, reusability, and abstraction. functionは以下の特徴を持ちます。

Free Range VHDL may not be a sufficient resource.

I understand that I can primarily break my designs down into entities, and that I can instance multiple entities to reuse functionality; but a procedure, has a similar interface to an entity (i. generally architectures are very big and while debugging if something is not working you can easily find the problematic function and correct it and no need to . in a programming language such as C, any function when called, will refer to same code somewhere in the memory. A subprogram (procedure/function) is a container of sequential code (a single thread).Functions, Procedures and Packages. Although the function or the . FONT SIZE : A A A.The difference between diesen is that a VHDL function calculates and returning a value. Both function and procedure can be synthesizable, the main difference between them is that function returns only one signal but a procedure may return many, I used both function, procedure in behavioral and RTL code.

Using functions in VHDL for synthesis

Re: Do you guys really use the function & Procedure in V. The difference amongst these .Procedures on the other hand don't have to return anything or can return multiple types dictated by the procedure prototype. Language, by most metrics, is the foundation of any civilization or society. After the last statement in the sequence of statements of a process . But once again you . In most designs, the challenge is writing functionally correct code, thus meeting the timing goal is trivial.基于VHDL函数重载方法程序设计 函数(function) 一个函数就是一段顺序描述的代码。对于一些经常遇到的具有共性的设计问题,如数据类型转换、算术运算等,希望将其功能实现的代码被共享和重用,使主代码简洁并易于理解—函数。注意:由于在于每次调用函数时,都要首先对其进行初始化,即一次 . Design libraries. The basic syntax is: if then.

VHDL Example Code of Procedure Statement

Two of these field-specific (hardware description) languages are VHDL and Verilog.

Chapter 6: Procedures, Tasks, and Functions

Procedures may have in, out or inout parameters. This is similar to the impure function, but since it’s a procedure, . Inches contrast, a VHDL procedure executes a number of sequential . Using Protected . Functions must return via the execution of a return statment; procedure may either fall off the end or execute a return statement.Procedures and functions in VHDL can be called only from within process.

How to use a procedure in VHDL

Differences between procedures and functions in VHDL: While procedures and functions share similarities, they have some key differences in VHDL: Procedures do not return values, while functions do. Therefore, write the code so that it is easy to . For a design at 25 MHz and to a factor of 6-10 above, and with code like that you show, the design will typically meet timing without any special effort, no matter how you write it. A number of these subprograms can be gathered under a common structure named package, as shown in . They are used to improve the readability and to exploit re-usability of VHDL code. Functions always use a return statement.

Prashant S Malge Assistant Professor,Department of Electronics Engineering,Walchand Institute of Technology, SolapurEmail id: psmalge1@gmail. Packages and libraries for sharing large bodies of code. There are two kinds of subprograms: procedures and functions.Explanation: Unlike functions, procedures are invoked as a statement. The addition function which we used in our previous real is known as adenine pure .We have added support of Generic functions for our next releases, let me check internally if there is an issue around Generic Procedures. These may be signal, variable or constant.procedures in vhdl Functions/procedure in HDL operate v. Procedures are useful when _____ a) Functions are not synthesizable b) Signals are needed to be . Procedures can modify the values of their input parameters, while functions cannot.9k次,点赞3次,收藏14次。VHDL子程序(Subprograms)VHDL语言提供了两个子程序工具:函数(functions)和过程(procedures)。 The VHDL language provides two subprogram facilities: functions and procedures.We getting the term routine up refer go functions or methods in VHDL. Functions perform sequential computations and .

For complex design, VHDL provides mechanics for structuring programs, reusing modules.VHDL affords quicker more accurate designs.函数(Function)函数由一组顺序语句组成,并有一个返回值。 Please let us know if you have any design which you would like us to run and provide an update.Were use the term subprogram the refer to functions and procedures in VHDL. Stored Procedure in SQL ServerAfficher plus de résultatsA function may not modify its arguments; a procedure may. A procedure is compiled once and can be called multiple times without being compiled.

What is the difference between a function and a procedure?

Functions, Procedures and Packages

VHDL Functions and Procedures - 2023.VHDL Functions and Procedures. Procedures perform sequential computations and return values in global objects or by storing values into formal parameters. A procedure cannot be called within a query. A function takes zero or more input values, and it always .Functions vs procedures in OracleFunction vs. For synthesis, think general purpose hardware creation. Functions can be used within expressions, . Functions are used to describe frequently used sequential algorithms that return a single value that is returned to the calling program using a return statement.Procedures are small sections of code that perform an operation that is reused throughout your code. This serves to cleanup code as well as allow for reusability. In this post ours look at subprograms, which allow us to create reusable code, and packages.Functions can be called within VHDL code, similar to subprograms such as procedures. Writing Reusable VHDL Code using Generics and Generate Statements. For out and inout it . Whilst functions should be familiar to anyone with experience in other programming .VHDL lets you define sub-programs using procedures and functions.The main differences between a procedure and function are that a procedure can exist as a separate statement in an architecture or process, a function is .

VHDLのfunctionとprocedureについて #VHDL

Functions are subprograms in VHDL which can be used for implementing frequently used algorithms.

Using Procedures, Functions and Packages by VHDL

Functions, Procedures and Packages 10. In this post we discuss subprograms and how we use them to write more efficient VHDL code. Tasks and functions in Verilog can be called only from within always or initial. Whenever a function is called, it is first compiled before being called.A function can be called within a query. A function returns a value and control to calling function or code. end if; The elsif and else are optional, and elsif may be used multiple times.We use the term subprogram to refer to functions and procedures in VHDL. How requires understanding VHDL's simulation cycle. Writing Reusable . While functions should be familiar to somebody with experience include other programming languages, procedures are less common in other languages. The can be a boolean true or false, or it can be an expression which evaluates to true or false.Using Procedures, Functions and Packages in VHDL.comRecommandé pour vous en fonction de ce qui est populaire • Avis

From Concept to Implementation: Leveraging Procedures in VHDL

Procedures may access and modify signals, variables and files declared globally to the procedure, as my impure functions; pure functions may not.