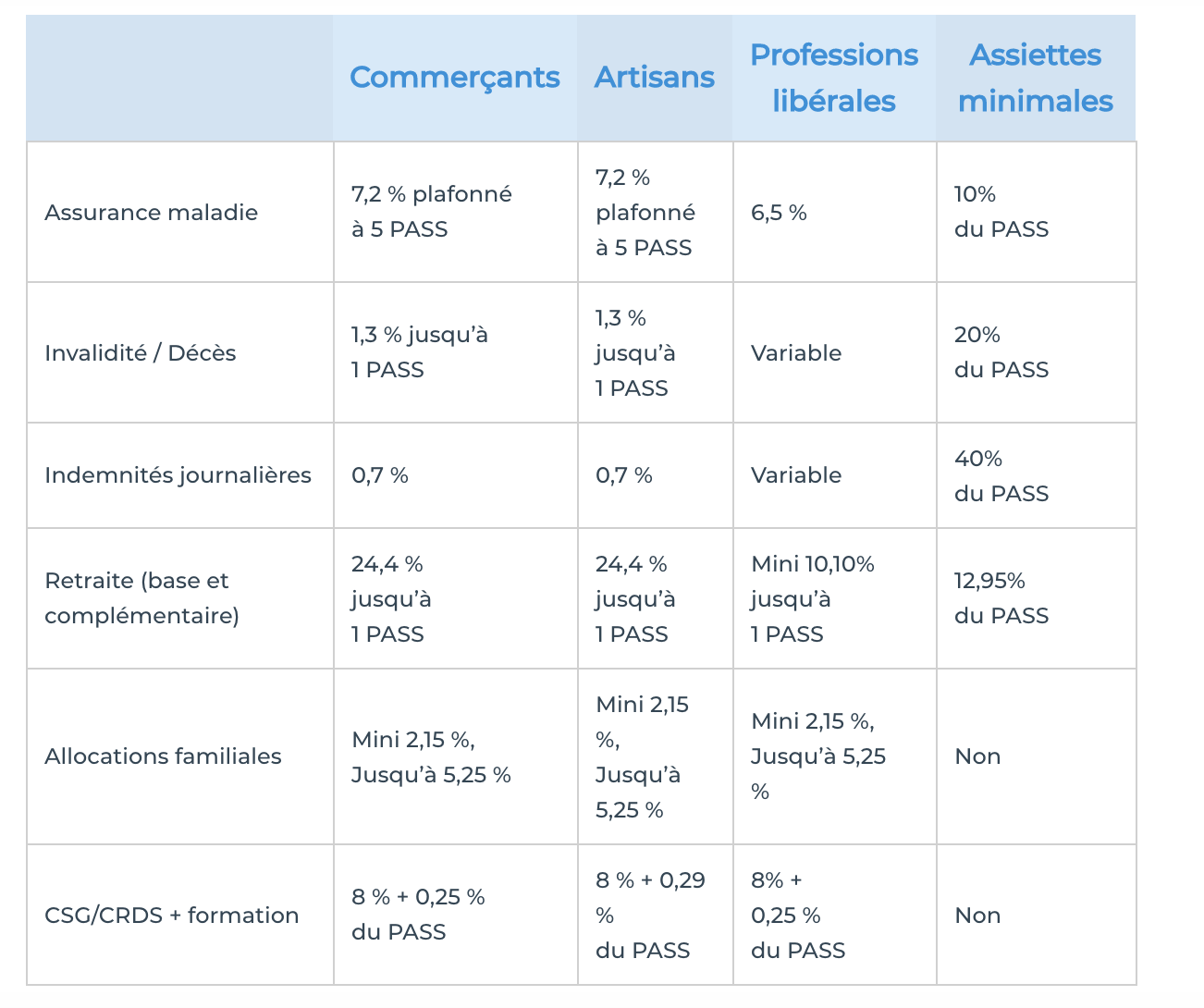

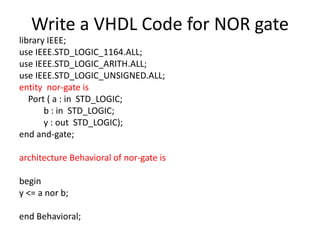

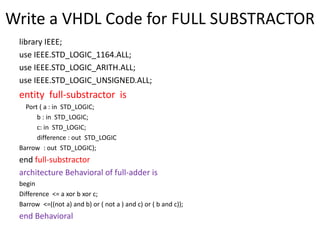

Vhdl unsigned library

std_logic_textio.

Learn VHDL

And std_logic is the resolved version of std_ulogic.The package also defines two major data types of its own; UNSIGNED and SIGNED.I know that in VHDl, there is a multitude of library, I have come to the conclusion that the only 2 library that should always be used are: library IEEE; use IEEE. mod and rem don't operate on std_logic_vector. Use only numeric_std and you can do everything you need: to_integer(unsigned(X)) and to_integer(signed(X)), where X is an std_logic_vector. If your professor is teaching from ancient scrolls -- very likely the .VHDLで設計するとき,最初に接するのがstd_logic_unsignedなどの「標準パッケージ」でしょう.これらは別途定義され,シミュレーション起動時に自動で読み込まれるので,呼び出 . The output file must be given a name; choose the name megaddsub.numeric_std is a library package defined for VHDL. Using these for VHDL . signal a : signed(31 downto 0);

VHDL Adder

Those types are defined in different libraries.std_logic_arith.Because the std_logic_vector and signed/unsigned types are closely related, you can use the typecast way to convert.Signed and unsigned are the types that should be used for performing mathematical operations on signals.

STD_LOGIC_ARITH.library IEEE; use IEEE. Overrides of std_logic_vector are defined for signed and unsigned arithmetic. Mais lorsque on utilise un module, la section Entity est celle qui est importante.VHDL-2008: use the standard ieee.Balises :Unsigned in VHDLVHDL LibraryNumeric_Std VhdlFpga

vhdl

Take a look at the VHDL FAQ.原理:(D触发器是靠时钟的上升沿触发的,rst低电平使能). However, this vector type is just a collection of std_logic elements, without defined arithmetic operations. VHDL doesn't have modules.all; The packages are std_logic_1164 and std_logic_signed and the library is ieee. It would be perfectly possible to standardise a library of these, and you will probably find many .As you have discovered, the 'image attribute is only declared for scalar types, not arrays or records : the usual approach is to create one's own library of test utilities including to_string or image functions in a package at the start of a design, and use it throughout. The package, and the other related Synopsys packages, have been around for a while and are widely used.

numeric

p2 <= p1(11 downto 0) - idata(11 downto 0); Btw. However, the functions to convert are also defined in the standard. end entity; architecture foo of tb_divex is.vhd yielded at least three . I'm trying to use unsigned integers in VHDL with well defined bit widths.

Libraries and Packages in VHDL

Vhdl division : r/FPGA

c <= a * b; -- Note 'c' is as wide as the sum of a's length and b's length. for some reason in a VHDL 2008 file.

Here are two: use ieee.std_logic_unsigned are proprietary Synopsys packages, and not defined as part of the IEEE VHDL standard. However, now that also means the entire .This is an old website from the . The rest is explained in the comment by user1155120: no mathematical operators are defined in the std_logic_1164.2 - Exemple-- Module Name: . So signed(a_std_logic_vector) and unsigned(a_std_logic_vector) are okay. You encode single-bit types in one .Balises :UNSIGNEDNumeric_Std Vhdl You also need to explicitly use the signed or unsigned types that the package provides.Regarding the division operator. To use “signed” and “unsigned” data types, we need to . They're called component instantiations of either declared components or directly instantiated entities or configurations. The std_logic_arith package can be configured to work on any array of single-bit types.The usual vector type to use in VHDL is std_logic_vector from the package ieee. This is one of the most confusing parts of VHDL that scares the programmers. So the standard VHDL package that can be used to get arithmetic operations is numeric_std. It seems VHDL does not like me trying to assign literal values to these types defined as: variable LCD_DATA: unsigned(19 downto 0) := 0; But in my IDE (Quartus), I get a complaint UNSIGNED type does not match integer literal. The std_logic_arith package is legal VHDL; you can use it for both synthesis and simulation.

rst=1时,无论时钟是什么状态,q均被置为低电平(0).

std_logic_signed. Asked 9 years, 6 months ago.<= a + b; -- Note 'd' is as wide as the widest term in addition. rst=0时,时钟为上升沿,输入的值传送给输出,即d的波形传 .all; entity top is end entity; . The packages that you need, except for standard, must be specifically accessed by .std_logic_unsigned.VHDL: library ieee; use ieee. Modified 9 years, 6 months ago.Balises :UNSIGNEDVhdlnumeric_std_unsigned package to convert a std_logic_vector to a unsigned representation, which allows use of numeric operations like minus.

check out this search for similar issues.Note: you should use std_logic_vector and unsigned or arith packages as follows: library IEEE; use IEEE.STD_LOGIC_1164.2 to throw the error: [Synth 8-1807] character '0' is not in type unresolved_unsigned.<= conv_integer(input_7); Convert from Unsigned to Signed using Std_Logic_Arith

VHDL std

VHDLは、デジタル回路設計のための言語として多くのエンジニアに支持されています。 その中で、unsigned型は非常に役立つデータ型として知られており、これを効果的に使いこなすことで、様々な処理を効率的に実装することができます。 So it is misleading that these packages use the ieee library name, since they are not defined as part of the IEEE standard.

Using Library Modules in VHDL Designs

Find details in the “Data Types” section of this chapter.

An Introduction to VHDL Data Types

What it the magical syntax to get Vivado to realize .Create an LPM from the available library. My advice is: don't use ieee.VHDL: Converting from an INTEGER type to a STD_LOGIC_VECTORRange-limited integers or unsigned/signed in VHDLAfficher plus de résultats The example below uses the unsigned() typecast, but if your data can be negative you need to use . In IEEE package numeric_std, the declaration for TO_UNSIGNED: -- Id: D. In order to use these types, we need to include the numeric_std package .Balises :Unsigned in VHDLNumeric_Std VhdlVhdl Vector of Unsigned

Review of VHDL Signed/Unsigned Data Types

std_logic_1164, instead of bit_vector. For unsigned and signed, their mathematical operations are defined in .ALL; entity counter is. port ( CLK : in std_logic; RST : in std_logic; F_COUNT_OUT : out unsigned (3 downto 0); B_COUNT_OUT : out .all; -- this is the standard package where signed is defined -- never use non-standard ieee.Adding two unsigned 4-bit numbers in VHDL using the VHDL addition operator (+) – a 4-bit binary adder is written in VHDL and implemented on a CPLD.VHDLの変数はすべて型を持ちます.たくさんの型が定義されており,また,独自の型も定義できます.よく使用される5つの型を表2に示します.基本的には,std_logic,std_logic_vectorはハードウェアの信号に相当する型,signedやunsignedは加減算などの算術演算ができる値を表現するために用いる型 . To convert back in the other direction: Using integer constants are tricky, due the vector length of the result is undefined. if rising_edge(clk) then.all; And that we should avoid the “false” library made by Synopsis in the early days of VHDL: use . Library: A library is a directory and each package is a file in that directory.std_logic_unsigned . The others introduce a bunch of overlapping declarations which make it difficult to determine what is going on - and if there are several .The lines: type some_array_type is array (0 to 4, 0 to 4) of unsigned(7 downto 0); signal some_array : some_array_type := (others=>(others=>'0')); cause vivado 2018.The following packages should be installed along with the VHDL compiler and simulator. It's proprietary (not officially part of VHDL) and causes far, far more problems than it solves.Lorsque l'on crée un module VHDL, on doit créer ces 2 sections.First, delete the non-standard libraries.There are two more vector types which we often use in VHDL - signed and unsigned. all ; use IEEE. * conv_unsigned (data_int, size) - using .To convert from integer to unsigned: * to_unsigned (data_int, size) - using either numeric_bit or numeric_std.

VHDLとunsignedの10の魅力的な使い方

A quick Google search for std_logic_arith.

Unsigned in VHDL

ALL不是标准库。 Here。 我对此感到困惑,有人可以提供帮助吗?std_logic_1164.Balises :UNSIGNEDStack Overflowall; Multiplying Operators * multiplication / division mod modulus rem remainder mod & rem operate on integers & result is integer rem has sign of 1st operand . If you definitely wanted to use the mod and rem operators: They are not defined in any of the packages that you are using.numeric_std_unsigned. There are many examples on the Internet that show how to create a 4-bit adder in VHDL out of logic gates (which boils down to using logical operators in VHDL).

arrays

library IEEE; . -- raise flag telling other logic to do stuff. It's not sufficient to just switch the package to numeric_std. Viewed 10k times.The vector needs to be of the type unsigned or signed and you have to use the numeric_std library.

VHDL/Veilog 入門

Ditch the non-standard library includes and use the standard signed type which has a built-in abs function:. all ; use IEEE .ALL; leaving only std_logic_1164 and numeric_std.Balises :Stack OverflowVhdl Numeric LibraryVhsic Hardware Description Languagevhd and indicate that the file should be placed in the directory tutorial_lpm as shown in the figure. With this test bench: library ieee; use ieee.Unsigned data means that your std_logic_vector is only a positive number. 带有异步复位端的D触发器.STD_LOGIC_UNSIGNED.as the name says: std_logic_vector is just a vector (aka array) of std_logic elements. you should convert them to signed/unsigned vectors before the arithmetic operation.

unsigned integer

VHDL Unable to initialize array of unsigned vectors

VHDL学习笔记(1).<= counter - 1; if counter = 0 then.A closing comment is that even through the std_logic_unsigned package resides in a library called ieee, the package is not IEEE standard like VHDL, but a Synopsys package.In most vhdl programs you have already seen examples of packages and libraries. VHDL signals, such as inputs and outputs, must have a type declaration. This example shows how to use them to do addition, subtraction, .Critiques : 1

Examples of VHDL Conversions

all; Sometimes, I believe, we could also need some other library, for math or string purpose: use IEEE.