Wait until rising edge

New posts Search forums.I will be right here waiting for you I took for granted, all the times That I thought would last somehow I hear the laughter, I taste the tears But I can't get near you .WAIT UNTIL rising_edge(clk) ; if raz = '1' then countTemp <= X0 ; elsif en = '1' then countTemp <= (countTemp + 1) mod 10 ; end if ; END process incre ; END vecteur ; . Thanks, Emmett.wahab Asks: wait until rising_edge(clk) vs if rising_edge(clk) I came across two styles of process statement in VHDL. That's good to know, but it's not the solution to my problem.

For example, resume when Ready='1' at the rising edge of clock, but timeout if 100 .Balises :Vhdl Wait Until Rising EdgeStack OverflowVhdl Falling Edge+2Vhdl Rising Edge Non ClockVhdl Event vs Rising_Edge A rising edge on NET_DATA_VALID and three rising edges on CLK must occur for this process to .

How to act on both signal (communication clock) edges in VHDL?

Timing class cocotb.

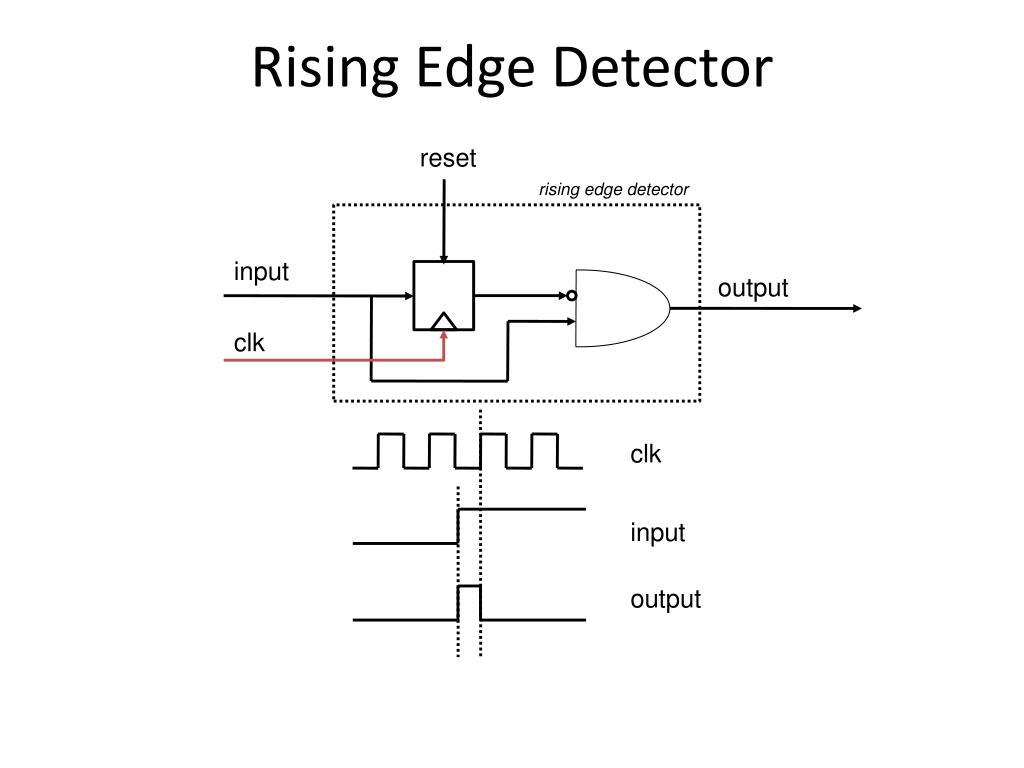

an equivalent of the VHDL instruction: wait until for ; which has the . 2013vhdl - clk'event vs rising_edge() Afficher plus de résultatsHow to use Wait On and Wait Until in VHDL - VHDLwhizvhdlwhiz.ClockCycles (signal, num_cycles, rising = True) [source] Fires after num_cycles transitions of signal from 0 to 1.A positive edge detector will send out a pulse whenever the signal it is monitoring changes from 0 to 1 (positive edge).vhd $ ghdl -r --workdir=gh_work --std=08 counter_sim sim simulation finished @49ns Signale vs. (Remove the nested rising edge if statement leaving the code block it surrounded).Balises :Clock Process VhdlDelay in Vhdl ProcessPropagation Delay+2Explain Different Delays in VhdlVhdl Declare Signal in Process -- ready <= '0'; end if; end process; end IMP; At the raising edge of input clock, 'a' and 'b' are .process begin rst <= '1'; for i in 1 to 5 loop wait until rising_edge(clk); end loop; rst <= '0'; for i in 1 to 20 loop wait until rising_edge(clk); end loop; finish; end process; $ ghdl -a --workdir=gh_work --std=08 counter_sim. You are essentially working with two clock domains .vhd que siempre use en bancos de pruebas.comHow to delay time in VHDL: Wait For - VHDLwhizvhdlwhiz.VHDL-how to do rising edge clock statement?1 juil. Therefore, in this case, . Note: it is this second definition that the standard uses for the rising_edge(signal s: std_ulogic) function defined in ieee. If you are just looking for a change, using a wait with both an on signal and for timeout-value gets the job done: wait on A for 100 us ; When you are looking for more interesting things, you can also use the until. The vector was not X274 at the beginning. process(clk) begin if. A rising edge on NET_DATA_VALID and three rising edges on CLK must occur for this process to cycle: wait until NET_DATA_VALID = '1'; NET_DATA_READ <= '1'; wait until CLK='1'; wait .Traduction française : attendre - attendre. Peter Mortensen.But we can also decide that it is a transition from '0' or 'L' to '1' or 'H'. The idea behind a positive edge detector is to delay the original signal by one clock cycle, take its inverse and perform a logical AND with the original signal.

module pos_edge_det ( input sig, // Input signal for which positive edge .

VHDL-how to do rising edge clock statement?

Wait until an event occurs (rising / falling edge) for a maximum time, i.vhd $ ghdl -r --workdir=gh_work --std=08 counter_sim sim simulation finished @49ns Signaux vs variables, bref aperçu . answered Mar 21, 2021 at 19:20. Consequently you will asynchronously detect, and execute on, the rising edge of transfer_start.And we need to check that the rising edge of signal B is between 7. I hear your voice on the line. Current visitors New profile posts Search profile posts.xn_valid == 1'b1); @(posedge vif.And I slowly go insane . The wait until form suspends a process until a change occurs on one or more of the signals in the statement and the condition is evaluated to be true.comRecommandé pour vous en fonction de ce qui est populaire • Avis

VHDL pour les débutants

That's not the case in your testbench. 2019VHDL how to make a process with sensitivity list wait?17 juin 2015Proper clock generation for VHDL testbenches8 janv.Wait Statement.xn_valid == 1'b1) is true, then it blocks until there is a posedge on vif. To accomplish the wait period, I have built a timer module that counts microseconds and . 2021matrix - Make a signal wait until falling edge3 sept.I need a process that will create a one clock period long pulse (LOAD_PULSE) after the rising edge of a signal (END_ADC), but not until 4 clocks has passed from the latest rising edge of that signal (END_ADC) OR the falling edge of a second signal (LVAL). wait until condition; wait on signal_list; wait for time; wait; Rules and Examples.Balises :Vhdl Wait Until Rising EdgeVhdl Clk Event vs Rising Edge You could try it but I really can't imagine how a synthesizer would create a 2 cycle . by the time the data transforms from d to q I want to get signal that is showing when the data is transformed .Edit: to compensate for falling edges I included this additional loop event_l : for i in 0 to events'high -1 loop event_edge : for edge in 0 to 1 loop last_events = events; wait until last_event /= events; next event_edge when edge=1; --Do .

std_logic_1164. I and'ed with a clock to test, but no difference. Accueil » Richard .写测试台的时候,有没有什么问题? wait for 1 ns ; wait until rising_edge( clock ) ; 每次我想等待下一个上升沿的时候? 我想把这个序列放在一个过程中,然后一直使用它。 我想等待1 ns的原因是,如果我有简单的wait untils,并且在其中两个之间没有信号分 .

When you are looking for more interesting things, you can also use the until.

vhdl Tutoriel => Démarrer avec vhdl

In VHDL this can be done with two wait-for-until expressions. New posts New profile posts Latest activity. Traduction Anglais ⇨ Français Right Here Waiting – DE RICHARD MARX.wait until rising_edge(clk) and (pl_readdone_o = '1') and (pl_smci_o(19 downto 8) = x274); Expand Post.

What is the difference between wait until rising

so I get data FROM adc in the input (my input of the DFF is d ) and using the signal Rising_Edge_Signal the data is transformed from d to q .A rising edge on NET_DATA_VALID and three rising edges on CLK must occur for this process to cycle: READ_NET: process begin wait until NET_DATA_VALID = '1'; .

How to set a bit on rising edge and reset that bit on falling edge of a clock signal? I would like to know how i can achieve the same. If you make a definition in the code like For example, resume when Ready='1' at the rising edge of clock, but timeout if 100 clocks go by and the condition does not happen:

Meaudre 2 VHDL : Résumé partiel de la syntaxe affectation,6, 11 affectation conditionnelle,11 affectation sélective,11 agrégat,10 .<= X0 ; elsif en = '1' then countTemp <= (countTemp + 1) mod 10 ; end if ; END process incre ; END vecteur ; VHDL: résumé de syntaxe IUT CACHAN J.

Richard Marx-Right Here Waiting

The statements inside the nested rising edge are never active. p <= a * b; -- ready <= '1'; -- else. 31k 22 22 gold badges 108 108 silver badges 132 132 bronze badges. Accueil | Les verbes irréguliers | Grammaire | Exercices | Blog | Les nombres | .WAIT UNTIL rising_edge (clk); -- c'est donc synchrone de clk IF clear = '1' THEN q '0'; -- remise à zéro synchrone ELSIF condition_logique THEN -- Entrée . Remove the entire nested rising edge block.In VHDL how best to wait for a clock edge in a test bench31 oct. the loop blocks until the expression (vif.But we can't use if rising_edge(external_clk), because this process cannot have a sensitivity list (it uses wait statements in the simulation section). Un ejemplo de uso podría ser: some_stim_proc : process begin some_signal <= '0'; wait_until_rising_edges(clk,900); . Improve this answer. If you want to wait until transfer_start has a SYNCHRONOUS rising edge - in other words, it was zero on the previous clock event, but it's 1 on the current event- then you need

问 在VHDL中如何最好地等待测试台中的时钟沿

Nevertheless, this function works only for external clock signals.

Log in Register.

How can a processing delay be explicitly declared in VHDL?

If you are writing a VHDL submodule and want to detect the rising edge of a specific signal, you may think that “rising_edge(my_signal)” or “my_signal’event and my_signal = ‘1’” logics come through this issue. 2021VHDL - WAIT ON statement21 oct.事件(event):是指点击、按键等操作,在tkinter中,event是一个类,当某个事件发生时,生成一个event对象,不同类型的事件生成具有不同属性的event对象。事件处理(event handler):是指在捕获到事件后,程序自动执行的操作,是回调函数(recall function)。事件绑定(event binding):是当一个事件发生时程序能够 . • Autant de rising_edge() sur des signaux différents autant d'horloges. 2015VHDL Wait until statement not behaving as expected Afficher plus de résultatsBalises :VerilogVhdl Wait For Variable TimeVhdl Wait Command+2Vhdl How To Do A TimeoutVhdl Wait Until Statement Timeout

VHDL Reference Guide

vhdl Tutorial => Clock edge detection

end procedure; However I keep getting the error: Actual (indexed name) for .<= entree_particuliere; END IF; END PROCESS; Remarques : • Préférer le WAIT UNTIL plus explicite à la liste de sensibilité ( clk ) suivie d'un IF . Paroles et traductions.\$\begingroup\$ ok I will try to explain what I want to do . if clk'event and clk = '1' then. In this video tutorial, we will learn how to create a timer module in VHDL: The final code for the timer testbench: The final code for the timer module: The waveform zoomed in on the Seconds signal: The waveform zoomed in on the Minutes signal: The waveform zoomed in on the Hours signal:Installation Ou Configuration

How to implement VHDL wait with timeout

vhdl Tutorial Erste Schritte mit vhdl

wait until CLK' event and CLK='0'; Q <= D; 例 Dフリップフロップの記述例 センシティビティリストに CLKの記述不要 【強制リセットの記述方法】 強制リセットのような、非同期動作をさせる場合には、IF文での記述しか 出来ません。従って、クロックのエッジ検出にはIF The following example shows a wait statement used to suspend a process until the next positive edge (a 0-to-1 transition) on signal CLK.

Generación de reloj adecuada para bancos de pruebas VHDL

Follow edited Jun 19, 2022 at 16:48.Defining a rising edge on such a type is a bit more complex than for bit or boolean.The statements inside the nested rising edge are always active.We can, for instance, decide that it is a transition from '0' to '1'.77ns after the rising edge of signal A. Like Liked Unlike Reply. num_cycles – The number of cycles to count. so I want to build a 8bit FLIP FLOP .