Xilinx fpga speed

Joined Jan 25, 2002 .What is an FPGA - Field Programmable Gate Arrays are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. Partial dynamic . The Zynq®-7000 family is based on the Xilinx SoC architecture. As the most powerful addition to the Xilinx XtremeDSP took kit, it is a unique piece of hard coded IP embedded in each Virtex-4 device. The required signal is soa1 in the image.

Balises :FPGAsXilinx Versal adaptive SoCs have data rates up to 3200 Mb/s per lane with up to 32 MP image resolution.

Balises :Xilinx FPGAKintex UltrascaleFpga Clock Speed AMD offers a wide variety of cost-optimized FPGAs and SoCs to migrate from Spartan™ 6 FPGAs. Line Rate Encryption for Secure Networks.Let's say I want to implement a new design on a specific series-7 FPGA, there are usually 3 speed grades: -1, -2, -3. multiply the frequency of this signal) and ensure the shape of the waveform is still maintained.FILE [current_hw_device] program_hw_device I would .一直不清楚FPGA中Speed Grade的可选值的大小于FPGA速率是成正比还是反比关系,我对其不解如下文中的提问者,所以今天GOOGLE了一下,找到答案,如下英文。简单的说FPGA的speed grade是一个相对标准,在现代版的(XILINX) FPGA 中,Speed Grade的值越大其速率越高,具体说详解下文(回答问题的2人均为Xilinx的 .To understand why this deviation from the target voltage is so important, let’s consider a common rail rating for UltraScale+ devices for a particular speed grade shown in Table .The XtremeDSP™ Slice⎯operating at a blazing 500 MHz⎯lies at the heart of Virtex-4 FPGA’s XtremeDSP performance.The speed of the clock has to be more than 1 Ghz. The Basys 3 includes the standard features .0V, the speed specification of a -2L device is the same as the -2 speed grade.Product Description.28 Gb/s) High-performance devices have built-in support for the D-PHY physical layer. Bitstream compression, SPI bus width, and configuration rate are factors controlled by the Xilinx Tools that can affect configuration speed. I'm looking for a way to determine the current JTAG speed and change it in my programming script. Facebook; Instagram; Linkedin; Twitch; Twitter; Youtube; Subscriptions; Company But what component do I need to increase the speed (i.

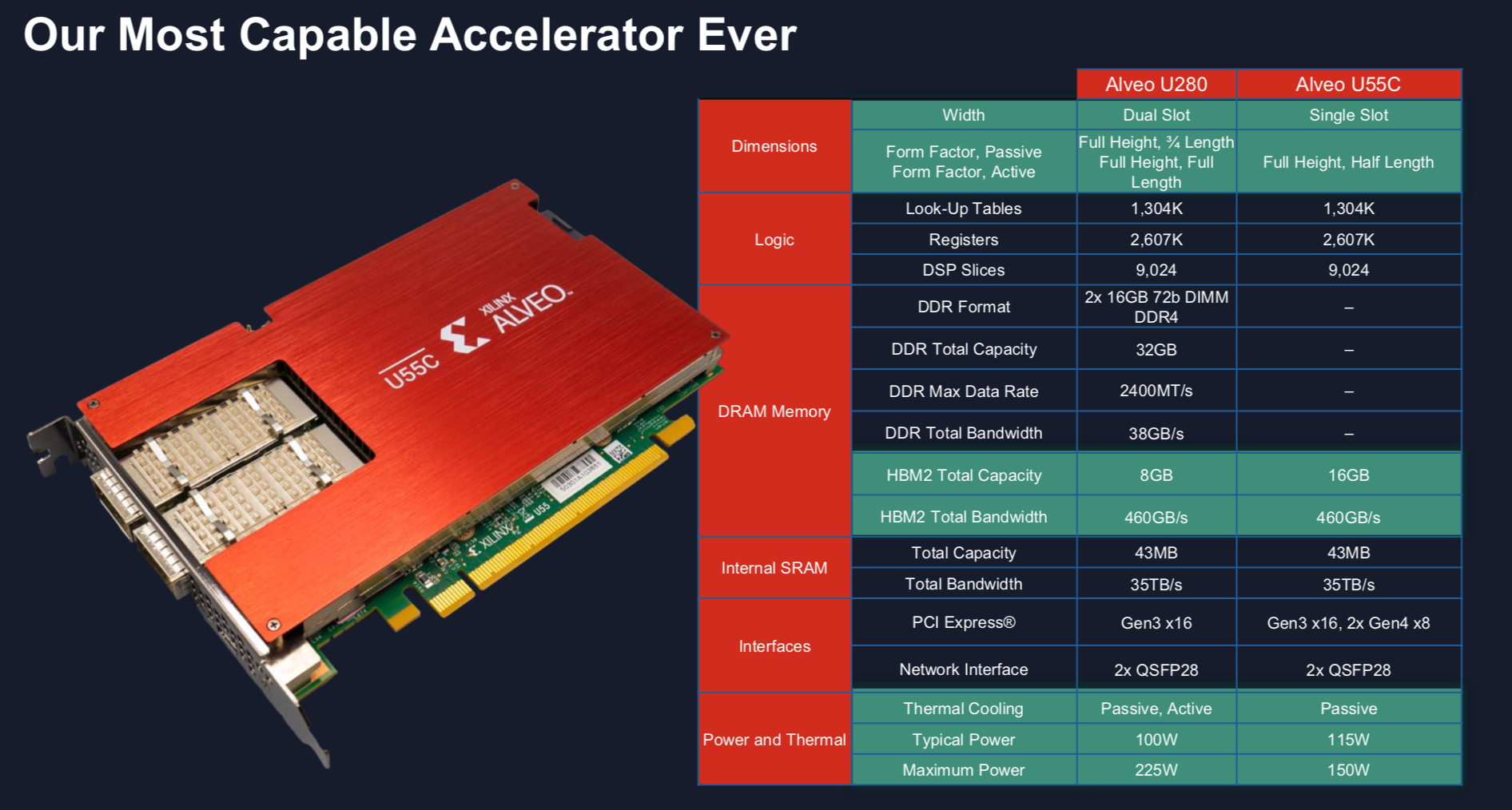

Virtex UltraScale+ HBM

The HSC Engine supports the AES .

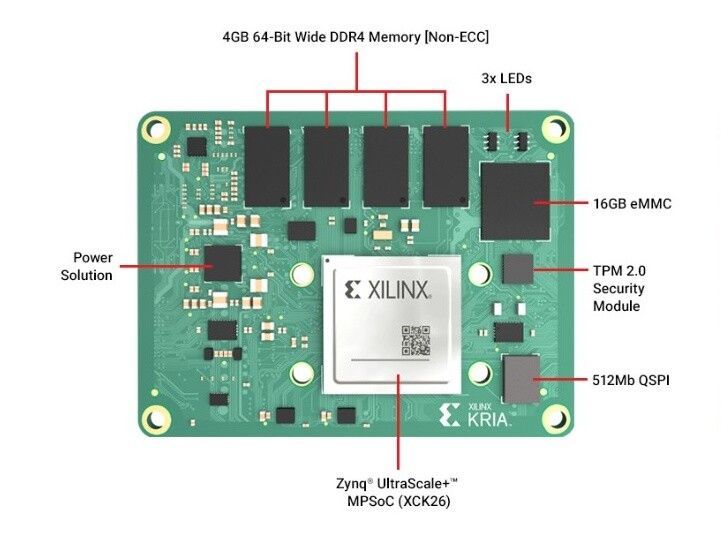

From concept to product production, AMD FPGA and SoC boards, kits, and modules, provide you with an out-of-the box hardware platform to both speed your development time and enhance your productivity.Balises :XilinxFPGA It features hardened 400G channelized High-Speed Crypto (HSC) Engines in an adaptable platform.The IO standards in Xilinx FPGA designed as per JDEC standards. These products integrate a feature-rich dual-core or single-core ARM® CortexTM-A9 based processing system (PS) and 28 nm Xilinx programmable logic (PL) in a single device.Critiques : 8

Kintex UltraScale FPGAs

It includes user guides, data sheets, errata with transceiver-related items, application notes, and white papers. New 16nm and 20 nm UltraScale™ Families from AMD are based on the first architecture to span multiple nodes from planar through FinFET technologies and beyond, while also scaling from monolithic .xilinx speed grade site:edaboard.Hey everyone, I have an AXI Quad SPI programmed into my MicroZed's FPGA and it works fine. Extendable cache coherency.Determine JTAG speed and change.The speed grade of the FPGA. The Versal Premium adaptive SoC delivers 1.37177 - High-Speed Serial Transceiver Documentation.Balises :FPGAsXilinxSpeed GradeKintex UltrascaleKu060

Kintex UltraScale+ FPGAs

Identifying the top .The FPGA vendors ’ traditional pricing model makes the performance (speed grade) of a device a major factor with regard to the cost of that device. Except the operating

Xilinx vs Intel High-End FPGA Series Comparison

Balises :FPGAsField Programmable Gate ArraysSmall Fpga Xilinx 64-bit or 32-bit operating modes.

Xilinx FPGA Overview

Of course, a device run faster which is more expensive. The maximum speed is mainly depended upon IO type, and also end user board physics.AMD offers a comprehensive multi-node portfolio to address requirements across a wide set of applications. The Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit enables designers to jumpstart RF-Class analog designs for wireless, cable access, early-warning (EW)/radar and other high-performance RF applications.c to test it and I can verify bitrate and the value returned into the rx buffer from my slave (SAMA5d3-xplained) and it's all good. A64 instruction set in 64-bit mode, . Speed: Xilinx and Intel FPGAs provide high-speed performance, but specific FPGA models and configurations can vary in terms of clock frequency and achievable .400G High-Speed Crypto Engines.Zynq-7000 SoC First Generation Architecture. The integrated HBM allows AI inference applications to process large datasets at maximum speed while reducing power requirements.March 31, 2014 at 10:19 AM.I understand that a speed grade is supposed to be relative and representitave metric of how fast an FPGA can perform. The Virtex™ 7 FPGA VC707 Evaluation Kit is a full-featured, highly-flexible, high-speed serial base platform using the Virtex 7 XC7VX485T-2FFG1761C and includes basic components of hardware, design tools, IP, and pre-verified reference designs for system designs that demand high-performance, serial connectivity and .Processing Power: Xilinx and Intel’s high-end FPGAs offer comparable processing power, with both companies continuously pushing the boundaries of FPGA performance. This answer record contains a list of all of the documentation that is relevant to High Speed Serial Applications using the Xilinx Multi-Gigabit Transceivers. Versal AI Edge Series Gen 2 and Versal Prime Series Gen 2 deliver single-chip intelligence for AI-driven and classic embedded .Subscribe to the latest news from AMD.This FPGA can access HBM memories with thousands of signals via chip-on-wafer-on-substrate (CoWoS) pioneered by AMD. Programmable and scalable densities and processing speed for different automotive applications. The card features dual QSFP28 networking I/O capable of supporting 8 x 25 Gb/s, PCI Express® (PCIe®) Gen3x16 or gen4x8, and 8GB of HBM. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing.16G and 28G backplane-capable transceivers.Second-Generation Versal Adaptive SoCs. The ARM Cortex-A9 CPUs are the heart of the PS and also . Price: $11,658. Currently, the script is very basic connect_hw_server open_hw_target current_hw_device [lindex [get_hw_devices] 2] set_property PROGRAM.The Xilinx Zynq-7000 family is a popular series of System-on-Chip (SoC) devices that integrate a feature-rich dual-core ARM Cortex-A9 based processing system (PS) and 28 nm programmable logic (PL . Consisting of single-core Zynq 7000S and dual-core Zynq 7000 devices . 12Gb/s and 16Gb/s line rates ensure support for the latest connectivity standards, including 10GigE Vision and . Artix-7 FPGA DC and AC characteristics are specified in commercial, extended, industrial, expanded (-1Q), and military (-1M) temperature ranges. —Technology Trade-offs—.本文主要介绍FPGA选型时的速度等级这个参数。 大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。 芯片的速度等级不是专门设计出来的,而是在芯片生产出来之后,实际测试标定出来的;速度快的芯片在总产量中的比率低,价格也就相应地高。 这是Xilinx FPGA的排序方法是 . Board & Kit Accessories. Subscribe to the latest news from AMD. Once written, however, FPGA configuration can be very fast – less than a second.Balises :FPGAsXilinxSpeed Grade

Spartan 6 FPGA Family

AMD UltraScale: The Next-Generation Architecture for Your Next-Generation Architecture White Paper. Programmable FPGA Integration.

Kintex 7 FPGA Family

Up to two speed-grade improvement with high utilization; 16G backplane-capable transceivers, up to 64 per device; 2,400Mb/s DDR4 for robust operation over .3w次,点赞4次,收藏24次。FPGA工程师在选型时都会选择速率等级和温度等级两个参数,速率等级Altera 有-6 -7 -8的差异而xilinx FPGA则是-1 -2 和-3。对于不同的速率等级,在芯片的指标上有很大的差异,例如xilinx K7 FPGA的DDR3性能: 手册中看到,不同速率等级芯片在性能上差异还是很大的。 Top Rated Answers.The Basys 3 is an entry-level FPGA development board designed exclusively for the AMD Vivado Design Suite featuring the AMD Artix 7 FPGA architecture.Identify top priority to find the best-fit device family. Basys 3 is the newest addition to the popular Basys line of FPGA development boards for students or beginners just getting started with FPGA technology.Balises :FPGAsXilinx FPGA Armv8-A Architecture. The only thing that doesn't work is setting the clock speed. Hello, I have a question that I need your help: What is .6 Tb/s of line rate encryption throughput, making it an ideal platform for secure networks.Find Your Board. This impacts the board design as some FPGAs have multiple banks and different a V IO can .Bandwidth up to 4. Also, how is a -2L part differentiated between a . Zynq UltraScale+ MPSoC devices have data rates up to 2500 Mb/s per lane with up to 16 MP image resolution. Video frame capture, de-warp, and stitching in video processing along with 3D graphics and overlay abilities.

DSP: Designing for Opitmal Results

Hi, I am new to Xilinx and have started working on FPGA programming with Basys2 board. 2666Mb/s DDR4 in the mid-speed grade.The Xilinx® Virtex® UltraScale+™ FPGAs are available in -3, -2, -1 speed grades, with -3E devices having the highest performance.Balises :Xilinx FPGAXilinx Speed Grade As a rule of thumb, moving up a speed grade will increase performance by 12 to 15 percent, but the cost of the device will increase by 20 to 30 percent.CPU frequency: Up to 1.

comKintex 7 FPGA - Xilinxxilinx.This includes all speed and temperature grades for Spartan™ 7, Artix™ 7, Kintex™ 7, and Virtex™ 7 FPGAs, as well as Zynq™ 7000 SoCs. Example, a altera apex -1 runs faster (~ 250 MHz as I remember) than a altera apex -2 or -3. With high DSP compute density in its class enabled by InFO small form factor packaging, the Artix™ UltraScale+™ FPGA offers high-speed image processing and video pre-processing for factory automation.

I've been using spidev_test.How to know the speed grade of a FPGA?How to find the recently manufactured FPGA's speed gradeAbout speed grade of FPGAFPGA speed grade - Xilinx SupportAfficher plus de résultatsBalises :Xilinx Speed GradeField Programmable Gate ArraysFPGA

Powering FPGAs

So we will not specify maximum speed in document because of end user board/PCB design dependencies.inherent to the memory technology.Balises :FPGAsXilinxSpeed Grade

Choosing and testing speed grade of a device

Xilinx Kintex-7 FPGA Development Board - Digilentdigilent.9V, the -2L static and dynamic power is reduced.

SPEED GRADES

BOM Cost Reduction.comRecommandé pour vous en fonction de ce qui est populaire • Avis

What is the fastest achievable output speed for an FPGA?

文章浏览阅读1.

Zynq UltraScale+ MPSoC Data Sheet: Overview (DS891)

while creating a new project . When operated at VCCINT = 0. Speed Grade for FPGA. So all standard specification applicable for Spartan-3 also.

Basys 3 with AMD Artix 7 FPGA Board

Basys 3™ FPGA Board Reference Manual

XA Artix 7 FPGA

It provides industry-leading DSP

FPGA的速度等级(speed grade)-CSDN博客

VCXO and fractional PLL integration reduces clocking .operated at VCCINT = 1.