Xilinx hls stream

Remove false dependencies.

Implementation and Significance of TLAST in AXI-Stream Interface

FPGA HLS stream与dataflow

pragma HLS stream

Can someone tell me how the arguements ap_axis are used? I was not able to find any documentation. Skip to content.

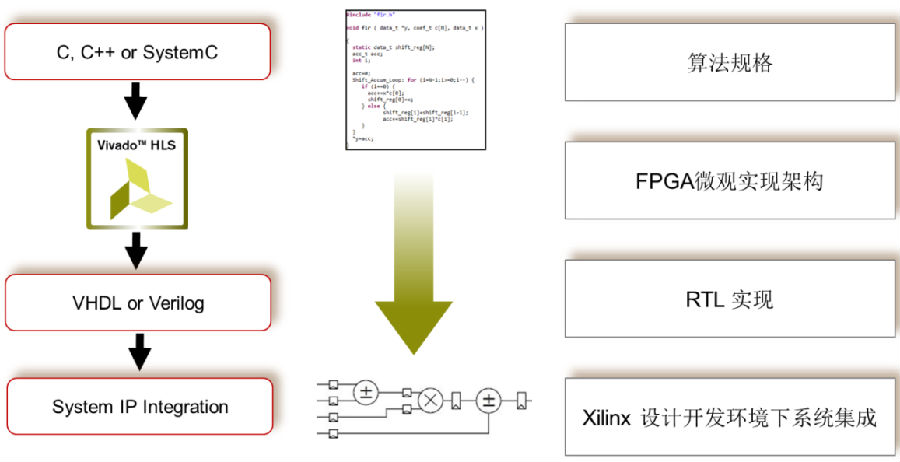

High Level Design

S00_AXIS' is input A and ''S01_AXIS'' is input B based on the . The following runs/benchmarks produce bad data.To make sure these are implemented as AXI Stream interfaces, we can use HLS pragmas to define the stream_in and stream_out as AXI Streams. #include ; #include ; #include ; typedef ap_axis DATA;; typedef hls:: stream AXI_STREAM;; void add_one (; AXI_STREAM & s_axis_in,; AXI_STREAM & m_axis_out; void add_one (; .Within a HLS dataflow region, all primitives connected via HLS streams can work in parallel, and this is the key to FPGA acceleration.AMD Technical Information Portal.

VIVADO HLS

However, this requires the use of a static variable to keep track of the number of samples received so far. Local buffer is passed to the second function which reads the buffer and streams it out.write () calls that really clutter the code. I want to model a fifo with non-constant depth, so I modified the void decimate_strm() function in the hls_stream project in Design Examples in Vivado_hls, (replacing the for loop with a while (!strm_in. 也就是说我们stream_tmp的长度不够,因为我们需要写两个数据,取一个数据.

HLS Tips and Tricks

This means that I redeploy the same two kernels every time I switch to a new benchmark. If you are a complete beginner to AXI and would like to become familiar with the essential terms and background, please see the tutorial AXI Basics 1.How to transfer part of a Xilinx HLS stream to another function? Asked 3 years ago. Models for streaming data structures—designed to obtain best performance and area (hls_stream. Tested with g++ (GCC) 8. So anyone please help me to create AXI stream multiplxer as shown in attached document (Custom_AXI stream_master slave_MUX.These cookies allow us to recognize and count the number of visitors and to see how visitors move around the Sites when they use them.This is simple example of Multiple Stages Vector Addition to demonstrate Array of Stream usage in HLS C Kernel Code. KEYWORDS: dataflow, hls::stream.The idea is to have a crossbar of streams between consumer and producer modules.

hls stream ap

Support Community.In this tutorial, you will work through the Vitis HLS tool GUI to build, analyze, and optimize a hardware kernel. One function reads the input line by line and stores one the line local buffer.

TVALID, which is 1 bit, 5.

#pragma HLS STREAM .HLS工具需要一个本地变量tmp 去缓存从端口A到端口B的数据, 另外只要你设置的端口变量类型是hls::stream< ap_axis都会有side channel, 赋值的时候也没必要把旁路信号一个一个对应上去,所有信号一起赋值的。 void example (hls:: stream < . In older HLS this was possible, and the documentation STILL states, that global .One method that seemed to work was to wrap the FFT call in a state machine that would collect the samples and store them in an array, then call hls::fft, and then send samples to the output stream. Sign in Product Actions.HLS Stream Library. I have two variables: void . User created FIFOs (from hls::streams and hls::stream_of_blocks between processes) may cause both deadlocks and/or low performance depending on their depths. Optionally recover resources through sharing.

zip) passes C Simulation, C Synthesis and C/RTL Co-Simulation.s5, Thanks for your time.

Design Help: HLS, AXI Streams, TLAST (and the DDS core)

Loading Application. Intro to Portal.The design (FIR_StaticCoeff. Fine tune operator sharing and constraints. Place the pragma in the C source within the boundaries of the required location.

HLS for a continuous streaming output device

HLS Tips and Tricks

Resources Developer Site; Xilinx Wiki; Xilinx Github; Support Support Community Modified 3 years ago. But their depths might be insufficient for optimal performance.0 on x86_64 GNU/Linux. Using the 1-bit flag stream to mark end of operation can trigger stream consumer as soon as the first row data becomes available, without known how many rows will be generated later. I also use a HLS Pragma to .

Using FFT with hls::stream

TDATA, which is 16 bits, 2.Introduction: In this tutorial we will explore the basics of how to create a custom IP with an AXI4-Lite interface in Vitis HLS.But in Vitis HLS (2021. Viewed 1k times. Note: The process for creating an IP with AXI in Vivado HLS is . Using the 1-bit flag stream to mark . TUSER, which is 1 bit, 4.I am trying to write a module that uses the AXI4 streaming protocol to communicate with the previous and next modules.empty()) ), as follows: The modules use the following communication signals: 1. A Tcl file is provided: run_hls. I see a struct with this name in ap_axi_sdata. In some cases it would be beneficial if a new port could be added without going through the full call chain. If you have multiple streams in a design is can be very hard to figure out which one to focus on based on the . First of all, what is the significance of the TLAST signal to AXI Stream protocol? Could there be remaining data in the hls:stream FIFOs? I do everything that they talk .Hi @thesoshne2 ,. Pipeline and Dataflow. H i g h - L e v e l S y n t h e s i s.

Dataflow Using Array of HLS Stream

#include patron_config.I've created an IP using Vitis HLS 2020. Loading application. My understaning of HLS is that both functions . The main problems are: Handling streams as references only.

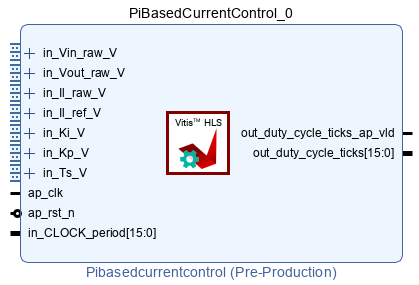

You can also learn how to set the port . When doing simulation, I got stuck because I'm not able to convert the AXI stream to image (Mat), I've tried the following and until this point it work: #include common/xf_headers.Please consider to resize the stream using the directive ‘set_directive_stream’ or the ‘HLS stream’ pragma. Vectorized types and operations (hls_vector. This means that when I have multiple FFT .HLS Dataflow allows user to schedule multiple task together to achieve higher throughput.默认情况下,顶层接口上的 hls::stream 是用 ap_fifo 接口实现的。 设计内部的 hls::stream 被实现为 深度为2的FIFO 。 优化指令STREAM用于更改此默认大小。 本 .) To avoid any .Hello, I am tried to create AXI stream master and slave custom IP core, Here i am found difficulty in port mapping of input and output signals.If you want to know the difference between hls_stream and AXI-stream types in Xilinx HLS, you can find the answer in this support topic. TREADY, which is 1 bit and goes towards the previous module, and 6. At a high level my goal is to generate a python script (using the PYNQ ecosystem) to program multiple DDS cores with phase increments and capture a user defined number of samples from them to PS memory.From the listed warnings, it would appear that more data is being read from the stream than is being loaded into the stream.tcl: Sets up the project and specifies what steps of the flow will be executed (by default only C simulation and C synthesis are . |Technical Information Portal. You are working through the Vitis kernel flow in the Vitis tool. If I do not, it doesn't correctly infer AXIS interfaces when I export from Vitis HLS.Contribute to Xilinx/Vitis-HLS-Introductory-Examples development by creating an account on GitHub.// Documentation Portal .h) Vector types. KEY CONCEPTS: Task Level Parallelism. This second version has 2 modes of operation: in mode 0, it performs FIR filtering on the input data: in mode 1, it reloads the coefficient . depth=: Relevant only for array streaming in DATAFLOW channels.1) I seem to need to change my top level function to this: void my_top(hls::stream& in_val, hls::stream& result); which then requires all sorts of extra . (Which makes my real project a mistery. 给tmp一个深度16的流.I am trying to figure out how to access a struct within an hls::stream and I cannot seem to figure it out.

Dataflow Using HLS Stream

TKEEP, which is 2 bits, 3.

Developer Site.Hi Folks, I'm trying to use the DDS core to teach myself about a combination of HLS, axi streams, and stream to DMA processes. I tried the directive and didn't work, I don't know why but some times if I mess around (copy/change) with the pragmas in Vivado HLS it doesn't update properly the directives to the ports, I ended up deleting all pragma port directives and generating them again and then I could get the two axi lite ports properly, .So for whatever reason, it would appear based on reading Xilinx documentation and breezing through the forums, that the TLAST signal is not included when you set up an AXI Stream Interface using pragmas.AMD Adaptive Computing Documentation Portal.I have created a simple AXI Stream core to add 1 to all inputs through the core. 但是内部的流被默认为深度为1,所以我们需要价格约束指令:.x), global variables became internal stuff, but this is not good. write (i << 8);} As you see, the type in question now is ' char ' and it does count upwards, so shifting left by 8 is not a problem. For example, I may want to generate a 16 bit stepped cycle in that just generates an AXIStream and cycles back to zero (I know this is straightforward in HDL) void (uint16_t *step_out) { #pragma HLS INTERFACE axis port . In this project where the two kernels are communicating, I can only get a successful run the first time on one benchmark. Toggle navigation.Define interfaces and data packing.Hey, is it still possible to use global variables as port? Since some version of Vivado HLS (I think it was 2018.void my_main (hls:: stream & m2i ) {#pragma HLS TOP; #pragma HLS INTERFACE axis port = m2i; unsigned char i; for (i = 0; i < 10; i\+\+) m2i.

Vitis HLS

This directory provides the C simulation model of HLS stream library. #include common/xf_axi. FIFO Sizing for Performance and avoiding Deadlocks.Temps de Lecture Estimé: 1 min

Vivado Design Suite User Guide: High-Level Synthesis

This helps us to understand what . (compute instructions and tasks parallelism) Partition memories and ports.