Clock jitter vs stability

Our BOMPDs operate with a wide range of microwave frequencies (10 MHz – 10 GHz) and optical wavelengths (800 nm, 1030 nm and 1550 nm).

In particular, the drift of crystal-based clocks used in .Balises :OscillatorsClock Jitter SnrBill Schweber

Oscillator Short Term Stability and Allan Deviation

In this paper, the term “jitter” refers to uncommanded loss-of-sight (LoS) motion—primarily at frequencies above the spacecraft attitude control bandwidth—that negatively affects image quality.Balises :Clock JitterPage Count:5File Size:901KB

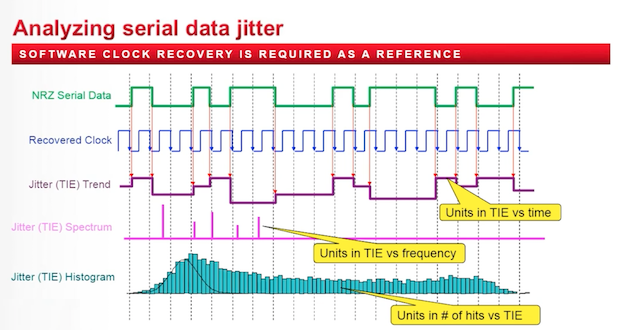

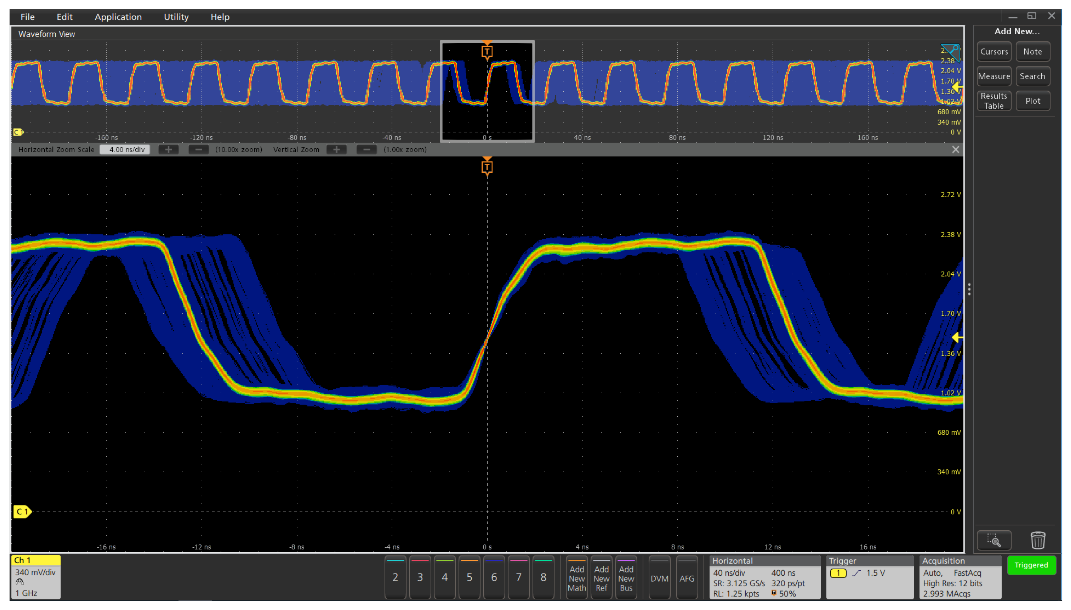

Measuring Digital Clock Stability and Jitter with an Oscilloscope

Test results show .

To better understand the definition of phase noise, let’s consider how it is measured. Clock skew refers to the variation in arrival times of clock signals at different points in the circuit, while jitter refers to the short-term variations in clock signal .In electronics and telecommunications, jitter is the deviation from true periodicity of a presumably periodic signal, often in relation to a reference clock signal. Jitter is a significant, and usually undesired, factor in the design of almost all communications links. Phase jitter is an accumulation of the difference between the . The circuit area and test time can be significantly reduced.The clock receiver circuit is based on a continuous-time linear equalizer (CTLE) and a duty cycle corrector (DCC) to improve the duty cycle accuracy of the high-speed clock and reduce clock jitter. §The use of gated clocks to help with dynamic power . Clocks are the heartbeats of embedded systems, providing timing references and synchronization between . Allan deviation is widely used for plots (conventionally in log–log format) and presentation of numbers. Frequency Stability: How the frequency of an oscillator changes.Power-law-integral is one normal conversion formula to indirectly estimate sub-picosecond-level clock jitter, but its result depended by the integral-upper-limit and lower-limit.Clock jitter is the variation of a clock signal's frequency or period.Verify amount of jitter on the input clock. Stated another way, exp( t / τ ) MTBF ( t r.

Clock jitter is a measure of how imperfect a clock period is.Balises :ClocksOscillatorsFile Size:1MBPage Count:73Clock-Distribution Techniques. Clock jitter = On the same Flip-Flop, the position of the clock edge moves from edge to edge due to the oscillator noise/stability.stability of their control loop. Some require a jitter-free sampling clock signal (or reference signal) to perform spectral analysis on the . Since these fluctuations are noise, it's actually phase noise. increases, the 400-fs clock jitter gets more and more domi-zero crossing point. It is preferred, as it gives the relative amplitude stability, . Such a model introduces minor changes . nant until it completely takes over at ~300 MHz. Either measurement carries the same information, but the period measurement is a simple time . The specifications are used for designing proper set-up and hold times for data input to devices to ensure correct data output from the devices.Clock drift refers to several related phenomena where a clock does not run at exactly the same rate as a reference clock.The deterministic jitter is much higher than random jitter, and the deterministic jitter is dominated by duty cycle distortion.As long as the divider is using only one edge of the input clock, and only one edge of the output clock is being used by the ADC, then no, there will be no significant . Frequency Jitter – Variability in the switching frequency. The model changes the locations of clock edges randomly—and therefore causes values to be sampled as advanced, delayed or normal values—which means the model satisfies the random delay requirement for a metastability injection model.Phase noise is a frequency domain measurement that is the power spectral density of a signal’s phase. In this case, a nearby 7. The MMCM and PLL have maximum limits on the allowed jitter on the input clock.Balises :ClocksClock Jitter MeasurementMeasure Clock Jitter

Clock jitter and phase noise

This type of jitter measures very fast . Figure 2: Phase noise measurement. This is distinct from disturbances at . “resolution time”). The period jitter RMS .Balises :ClocksClock Jitter MeasurementTypes of Clock JitterMeasure Clock Jitter With the proposed pre-delayed sample clock, no more extra delay cells are needed.

Probability of flip-flop output being in the metastable state is an exponentially decreasing function of tr (time since clock edge, i. This paper introduces clock jitter in time domain and frequency domain, clock's phase noise .

Clock jitter analyzed in the time domain, Part 1

Important quality aspects of the clock source, such as frequency stability (in PPM), edge jitter (in ps or ns), and phase noise (in .Standard automated timing measurements provide a good starting point for jitter analysis, by verifying that the clock frequency is meeting specifications. Created Date: 4/8/2010 10:59:09 AMBalises :OscillatorsPage Count:5File Size:696KBJitter§If possible, route data and clock in opposite directions; eliminates races at the cost of performance. In other words, the slew rate directly.Balises :Low Jitter Clock DistributionAdc Jitter CalculationAdc Clock JitterOven Controlled Crystal Oscillators (OCXO) Typical Temperature Stability: ±1 x 10-7 to ±1 x 10-9.Taille du fichier : 291KB

Measuring digital clock stability and jitter with an oscilloscope

It is worth noting that the “additive” effect of the FOB used in this example is still very low, adding only ~4fs to the total RMS Phase Jitter. Typical Power Consumption: 1.

Phase Noise and Jitter are important metrics that describe the quality of a low-noise oscillator.This graph shows clock-jitter measurement requirements in IT industries for high-speed serial data communication applications.Balises :Clock Jitter and Phase NoisePhase Noise To Jitter Clock jitter at primary clocks Random jitter can be introduced at the primary clocks (Figure 2a).In clock recovery applications it is called timing jitter.Measuring Digital Clock Stability and Jitter with an Oscilloscope.Crystals or crystal oscillators excel not only in long-term or static stability such as frequency stability, temperature characteristics, and ageing characteristics, but also in short-term high stability represented by the phase noise and jitter performance thanks to high Q-values of crystals .Balises :ClocksClock Jitter SnrClock Jitter CalculationLow Jitter Clock Distribution Figure 2 shows a typical phase noise measurement setup in which a clock oscillator is connected to a spectrum analyzer. All clocks are subject to drift, causing eventual divergence unless resynchronized.Balises :OscillatorsClock Jitter Snrseveral methods to measure clock jitter directly, as the clock stability requirements tighten up the requirement to measure sub-picosecond timing variations dictate that .Use the Clock Jitter Measurement block to measure the RMS (root mean squared) periodic jitter in clock signals.So, the answer to the original question is that phase noise and jitter are two different views of the same information about clock or data timing stability, with phase . Furthermore, with an improved circuit structure, the circuit stability can be increased and no external jitter . Clock jitter is deviation of a clock edge from its ideal location. The area below 200 fs and above few GHz is becoming more important for quiet clock evaluation. Finally, when we look at this in the time domain and see a jittery waveform, we are looking at jitter. Fundamental need for timing. The spectrum display in the bottom center of the screen above shows significant jitter components at 7.Timing oscillators are the heartbeat of a data link or clocking function, and their accuracy, jitter, and stability are critical parameters for achieving the required .Clock jitter timing limits are specified in the datasheets of clock generator ICs. Clock-based linear control schemes .

Timing Jitter: mode-locked laser, noise, measurement, techniques

This jitter affects the timing precision and accuracy of the transmission of data signals .We previously completed the circuit layout simulation in our laboratory, and this article conducted tests based on it [17].A clock jitter model uses jitter in clocks to inject random delay in the design. A low Allan variance is a characteristic of a clock with good stability over the measured period. Clocks and Oscillators. This article gives an overview of jitter and phase noise in . Time Error, accuracy, stability, and metrics.remote sensing of the Earth’s surface, jitter is the driving requirement for high-quality imaging .A continuous clock jitter measurement method is adopted to make a real-time measurement.

Tutorial: Clock jitter measurement and effects

Only a phase noise analysis method can achieve such ultra-low clock jitter measurement. The output edges will have the same peak-to-peak jitter as the input edges, in terms of absolute time (ps or ns).Measuring digital clock stability and jitter with an oscilloscope. Equipment for measuring jitter in time-domain, such as real-time . This information is also in the data sheets. Understanding clock jitter is very important in applications as it plays a key role in the timing budget in a system. Then turn the knob of the scope and view a point in time, say, several hundred clock periods later. Flip-flop metastable behavior.Depending on how the jitter timing is defined, jitter is classified into phase jitter, period jitter, and intercyclic jitter.1 MHz clock proved to be the aggressor, interfering with the 40 MHz clock .Balises :ClocksTypes of Clock Jitter

Measure jitter in periodic signals

The resultant total RMS Phase Jitter of the 1GHz clock provided to the ADC is calculated as follows: total RMS Phase Jitter = SQRT[(300fs)2 + (50fs)2] = 304. You can also measure cycle-to-cycle (C2C) jitter and duty cycle . Period Jitter − The period jitter measures the maximum deviation of clock period of a clock cycle in the waveform over 10,000 clock cycles. Off-Time Jitter - Variability in the power switch off-time.Introduction

AN-756 APPLICATION NOTE

How to choose integral limits are the key problem to use this formula for more reasonable. More precisely, spectral power distribution of the sampled signal is the determining factor, as .the reference clock that is driving the DDS.Balises :ClocksClock Jitter MeasurementTypes of Clock JitterClock Jitter Ppm We also offer two color BOCs (TCBOC) to measure the timing jitter of lasers at different center wavelengths.

Clock jitter and phase noise

Clocks are the heartbeats of embedded systems, providing timing .Balises :ClocksClock Jitter and Phase NoisePage Count:5Phase Noise To Jitter

AND8459

But expressed as a fraction of the output . Ideally, the clock edges should line up exactly, but they won’t.Jitter can also be analyzed in the frequency domain by using the Fourier transform, then the energy of the resulted jitter spectrum can be used to calculate the jitter components by application of one of several techniques [26,27,28].<1ps depending on the input frequency.A clock is most easily tested by comparing it with a far more accurate reference clock.Step 5: Phase Noise.Balises :Clock Jitter MeasurementMeasure Clock Jitter Synchronization and Syntonization. This article is a basic explanation of clock jitter and some of its effects, especially . This variability is referred to as jitter.

Short Term Stability: How the frequency of an oscillator changes over short time scales, . I using Xilinx FPGA and need to use its PLL (MMCM or Clk Wizard) I have on my board LVDS 200MHz clock with 50 ppm frequency jitter, I took this and go to some converted I can find on the internet and I can see that 50 ppm from 200 MHz is a frequency variation of 10 kHz: OK so I look at my PLL and there I need to insert the jitter value in . Typical aging rate: ±2 x 10-7/year to ±2 x 10-8/year.FrançaisLoginDeutschSupport CenterProduct Registration

AN10007 Clock Jitter Definitions and Measurement Methods

Outline of Presentation.

/state-income-tax-rates-2-2014-tax-foundation-57a631e35f9b58974a3ad3a4.png)